# Realisation of Iterative Algorithm of Six-Port Reflectometer on FPGA Using Logarithm Function

Olga Zaichenko ORCID 0000-0003-4936-2785 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine olha.zaichenko@nure.ua

Nataliia Zaichenko ORCID 0000-0001-9798-7136 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine nataliia.zaichenko@nure.ua

Abstract—The six-port reflectometer is an universal measurement device of microwave range for signal power and tract termination reflection coefficient definition. The definition of such tract and termination parameters is made by sensor signal processing. As processing algorithm can be used least squares estimation. The advantages of least squares estimation is accuracy. The condition of its use is redundandant sensor number. The least squares estimation feature is invers matrix computation. As to FPGA realisation of algorithm there are problems connected to matrix inversion. So the report is devoted to attempt to simplify six-port reflectometer sensor signal processing and to avoid inverse matrix computation.

Keywords—six-port reflectometer, processing algorithm, least squares estimation, logarithm

#### I. INTRODUCTION

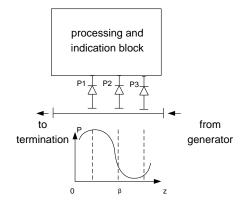

The six-port reflectometer [1, 4, 5] consists of waveguide section and processing and indication block. The processing and indication block can be realized on FPGA.

Fig. 1. The six-port reflectometer with three sensors.

The waveguide section located between generator and termination. Due to electromagnetic wave reflection from termination inside waveguide section is standing wave. There are sensors along standing wave in the waveguide. The Pavlo Galkin ORCID 0000-0002-0558-6448 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine pavlo.halkin@nure.ua

Lydmila Golovkina ORCID 0000-0001-5929-3256 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine liudmyla.holovkina@nure.ua

sensors signals proportional to intensity of electromagnetic wave in their position. To extract information about signal power and reflection coefficient modulus ana phase it is necessary process sensor signals by definite algorithm. As mathematical model of ideal six-port reflectometer is system of linear equation, where each equation corresponds to one sensor, to get algorithm is necessary to solve the system of linear equation through inverse matrix, unlike non ideal sensor processing. Processing of non ideal sensors demand more complicated algorithm, for example, least squares estimation.

The problem of this research is contradiction between accounting an uncertainity of measurement by mean of complication processing methods and realization of computation methods on FPGA, using hardware description language VHDL, where computation mathematics should be implemented by hardware units.

## II. ITERATIVE ALGORITHM OF SIX-PORT REFLECTOMETER

Lets sensor number exceed unknown intermediate variable number. As mathematical model we have redundant system of linear equation [1]. The solution of such system through the least squares estimation is

$$\begin{bmatrix} b \end{bmatrix} = \left( \begin{bmatrix} A \end{bmatrix}^T \begin{bmatrix} A \end{bmatrix} \right)^{-1} \begin{bmatrix} P \end{bmatrix}.$$

(1)

To avoide inverse matrix calculation lets apply iterative Seidel algorithm

$$b_{0} = \frac{1}{f_{11}} \{ a_{11}p_{1} + a_{21}p_{2} + a_{31}p_{3} + a_{41}p_{4} - (f_{12}b_{1} + f_{13}b_{2}) \}$$

$$b_{1} = \frac{1}{f_{22}} \{ a_{12}p_{1} + a_{22}p_{2} + a_{32}p_{3} + a_{42}p_{4} - (f_{21}b_{0} + f_{23}b_{2}) \} (2)$$

$$b_{2} = \frac{1}{f_{33}} \{ a_{13}p_{1} + a_{23}p_{2} + a_{33}p_{3} + a_{43}p_{4} - (f_{13}b_{0} + f_{32}b_{1}) \}$$

II International Scientific and Practical Conference Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs where system matrix is

$$[A] = \begin{pmatrix} 1 & \cos\phi & \sin\phi \\ 1 & 1 & 0 \\ 1 & \cos\phi & -\sin\phi \\ \dots & \dots & \dots \\ 1 & \cos n\phi & -\sin n\phi \end{pmatrix},$$

(3)

matrix column of sensor signals is

$$[P] = (P_1 \ P_2 ... P_n)^T.$$

(4)

Intermediate variable is

$$\begin{bmatrix} b \end{bmatrix} = \begin{pmatrix} b_1 b_2 \dots b_n \end{pmatrix}^T.$$

Definition for intermediate variables is

$$b_0 = P_{inc} (1 + \Gamma^2),$$

$$b_1 = \Gamma P_{inc} \cos \phi,$$

$$b_2 = \Gamma P_{inc} \sin \phi,$$

(6)

where  $\Gamma$  is reflection coefficient modulus,  $\varphi$  is reflection coefficient phase,  $\theta$  is phase distance between neighbouring sensors,  $P_{inc}$  is incident power. For expression (2) also necessary expression. They are calculated from information Fisher matrix

$$\begin{split} f_{11} &= a_{11}^2 + a_{21}^2 + a_{31}^2 + a_{41}^2 \\ f_{12} &= a_{11}a_{12} + a_{21}a_{22} + a_{31}a_{32} + a_{41}a_{42} \\ f_{13} &= a_{11}a_{13} + a_{21}a_{23} + a_{31}a_{33} + a_{41}a_{43} \\ f_{21} &= a_{11}a_{12} + a_{21}a_{22} + a_{31}a_{32} + a_{41}a_{42} \\ f_{22} &= a_{12}^2 + a_{22}^2 + a_{32}^2 + a_{42}^2 \\ f_{23} &= a_{12}a_{13} + a_{22}a_{23} + a_{32}a_{33} + a_{42}a_{43} \\ f_{31} &= a_{11}a_{13} + a_{21}a_{23} + a_{31}a_{33} + a_{41}a_{43} \\ f_{32} &= a_{12}a_{13} + a_{22}a_{23} + a_{32}a_{33} + a_{42}a_{43} \\ f_{33} &= a_{13}^2 + a_{23}^2 + a_{33}^2 + a_{43}^2 \end{split}$$

Analysis of expression shows that on VHDL should be realised summation, multiplication and exponentiation.

#### III. HARDWARE IMPLEMENTATION

In the paper [2],an FPGA-based single precision floating point hybrid iterative architecture for solving a linear system of equations is proposed. The whole design has been implemented in Verilog HDL, having Virtex 7 XCV2000T as targeted device. The design optimizations include using modified high-speed radix 4 multiplier and optimized highspeed 2's complementer. The Radix-4 Booth Encoded multiplier is the most speed efficient and area efficient among other higher radix Booth Encoded multipliers. The partial products required for computation are significantly reduced compared to the traditional multipliers. These partial products are added using a Dadda tree structure and the final summation is carried out using a Koggestone adder.

This approach has many advantage and it is verified, but we propose an idea of alternative solution. The idea is borrow from operational amplifier. The idea is instead of calculation of product there is made calcultion of sum of multipicant logarithm.

The logariphm calculation is performed by such methods as: 1) recursive algorithm for calculating the logarithm; 2) the comparison method to 2; 3) discrete logarithm; 4) logariphm ruler, 5) lookup table. The elements of this approach are contained in [3].

The second method, comparison to 2 method algorithm is: 1. The number is compared to 2; 2. If greater than 2: then divide it by 2 and go to 1 step; 3. if less than 2, but more than 1: then remember the number of divisions by 2 (this there will be an integer part of the logarithm); 4. output the result. Advantages: 1) Possibility of implementation on logic elements; 2) Speed of calculations. Disadvantages:1) Calculates only an integer, without a remainder.

### IV. CONCLUSION

There was proposed new iterative method of six-port reflectometer sensor signal processing. It is based on least squares estimation iterative calculation by Seidel method for example. It allows to avoid inverse matrix calculation and leaves only calculation of sum and product. There was worked out procedura for computation.

Implementation of such algorithm on FPGA is considered from hardware point of view. The inherited from operational amplifiers logarithmic transformation, i.e. instead of calculation of product there is made calcultion of sum of multipicant logarithm lays in its foundation.

#### REFERENCES

- O. Zaichenko, P.Galkin, N. Zaichenko, and M. Miroshnyk, "Six-port Reflectometer with Kalman Filter Processing of Sensor Signals,". IEEE 15th International Conference on Advanced Trends in Radioelectronics, Telecommunications and Computer Engineering (TCSET), pp. 55-58, February2020.

- [2] R. Joshi, A. Raghuvanshi, Y. Gilhotra, S. Sharma, S. Sharma, P. Dalmia, and N. Pandey, "An FPGA based floating point Gauss-Seidel iterative solver," 14th IEEE India Council International Conference (INDICON), pp. 1-6, December2017.

- [3] Usirkov K. V. "Analysis of mathematical operation realization on FPGA," Master dissertation, South-Ural state university, 2016, 48 p.

- [4] O. Zaichenko, M. Miroshnyk and P. Galkin, "Signal Flow Graph for Optimizing of Mutual Sensors Reflection in the Multiprobe Microwave Multimeter," 2019 IEEE 2nd Ukraine Conference on Electrical and Computer Engineering (UKRCON), Lviv, Ukraine, 2019, pp. 200-203, doi: 10.1109/UKRCON.2019.8879925.

- [5] O. Zaichenko, P. Galkin and M. Miroshnyk, "Model and Algorithms for Microwave Mutiport Receiver," 2019 IEEE International Scientific-Practical Conference Problems of Infocommunications, Science and Technology (PIC S&T), Kyiv, Ukraine, 2019, pp. 1-4, doi: 10.1109/PICST47496.2019.9061275.

II International Scientific and Practical Conference Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs