# II International Scientific and Practical Conference

# Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs

# MC&FPGA-2020

**Conference Proceedings**

Kharkiv, Ukraine June 25-26, 2020 II International Scientific and Practical Conference «Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs» MC&FPGA-2020, Kharkiv, Ukraine, June 25-26, 2020. – Kharkiv, NURE. – 60 pp.

There proceedings depict: mathematical modeling of information signals and systems; hardware description languages; systems of computer aided design of devices on microcontrollers, microprocessors and FPGAs; features of device development on microcontrollers and microprocessors; aspects of the development of devices in the FPGA; architecture and microprocessor technology; the problem of improving the quality of training specialists.

# Papers are presented in authors' edition.

Edition prepared of the Department of Microprocessor Technologies and Systems Faculty of Information Radio Technology and Technical Information Protection of the Kharkov National University of Radio Electronics with the support of the State Scientific Institution "Institute of Education Content Modernization" of the Ministry of Education and Science of Ukraine.

Head of the Department of Microprocessor Technologies and Systems Phone: +38 (050) 4061-220 E-mail: mcfpga@nure.ua , iryna.svyd@nure.ua Conference on Web: mcfpga.nure.ua

# Committees

| Valerii<br>Semenets        | Chair of the program committee, chair of the organizing committee, doctor of technical sciences, professor, rector of KhNURE (Kharkiv, Ukraine).                                                                                                                                                                        |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Igor Ruban                 | Vice Chair of the Program Committee, Member of the Organizing Committee,<br>Doctor of Technical Sciences, Professor, First Vice-Rector of Kharkiv National<br>University of Radio Electronics (Kharkiv, Ukraine).                                                                                                       |

| Murad Anver<br>oglu Omarov | Vice Chair of the Program Committee, Member of the Organizing Committee,<br>Doctor of Technical Sciences, Professor, Vice-Rector on International Cooperation<br>of Kharkiv National University of Radio Electronics (Kharkiv, Ukraine).                                                                                |

| Iryna Svyd                 | Vice Chair of the Program Committee, Member of the Organizing Committee,<br>Candidate of Technical Sciences, Associate Professor, Head of Department of<br>Microprocessor Technologies and Systems of Kharkiv National University of Radio<br>Electronics (Kharkiv, Ukraine).                                           |

| Paweł<br>Komada            | Member of the Program Committee, Ph.D. Eng. assistant professor, Deputy Director<br>of the Institute for General Affairs Lublin University of Technology, Institute of<br>Electronics and Information Technology, (Lublin, Poland).                                                                                     |

| Nikolai<br>Listopad        | Member of the Program Committee, doctor of technical sciences, professor, Head of<br>Department of Information Radio Technologies Belarusian State University of<br>Informatics and Radioelectronics (Minsk, Republic of Belarus).                                                                                      |

| Vahid<br>Meghdadi          | Member of the Program Committee, professor, professor the University of Limoges (Limog, France).                                                                                                                                                                                                                        |

| Serhat Şeker               | Member of the Program Committee, Prof. Dr., Dean of Faculty of Elecrical – Electronis Engineering the Istanbul Technical University (Istanbul, Turkey).                                                                                                                                                                 |

| Sergey Sakalo              | Vice Chair of the Organizing Committee, Member of the Program Committee,<br>Candidate of Technical Sciences, Associate professor, Senior Researcher, Dean of<br>Faculty of Information Radio Technologies and Technical Information Security of<br>Kharkiv National University of Radio Electronics (Kharkiv, Ukraine). |

| Aleksandr<br>Korotkevich   | Member of the Organizing Committee, Candidate of Technical Sciences, Associate<br>Professor, Dean of Faculty Radio Engineering and Electronics Belarusian State<br>University of Informatics and Radioelectronics (Minsk, Republic of Belarus).                                                                         |

| Vladimir<br>Kartashov      | Member of the Program Committee, Member of the Organizing Committee, doctor<br>of technical sciences, professor, Head of Department of the Media Engineering and<br>Information Radio Electronic Systems of Kharkiv National University of Radio<br>Electronics (Kharkiv, Ukraine).                                     |

| Ivan Antipov               | Member of the Program Committee, Member of the Organizing Committee, doctor<br>of technical sciences, professor, Head of Department of Computer Radio<br>Engineering and Technical Information Security Systems of Kharkiv National<br>University of Radio Electronics (Kharkiv, Ukraine).                              |

| Olena<br>Voloshchuk        | Member of the Organizing Committee, Ph.D, Assistant Rector of Kharkiv National University of Radio Electronics (Kharkiv, Ukraine).                                                                                                                                                                                      |

| Tetiana<br>Tkachova        | Member of the Organizing Committee, Candidate of Technical Sciences, Associate<br>Professor, Chief of Department of International Relations of Kharkiv National<br>University of Radio Electronics (Kharkiv, Ukraine)                                                                                                   |

| Volodymyr<br>Kobziev | Member of the Program Committee, Member of the Organizing Committee,<br>Candidate of Technical Sciences, Senior Researcher, Associate Professor of the<br>Department of Applied Mathematics of Kharkiv National University of Radio<br>Electronics (Kharkiv, Ukraine).                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oleg Sharpan         | Member of the Program Committee, Doctor of Technical Sciences, Professor,<br>Professor of the Department of Theoretical Foundations of Radio Engineering at the<br>National Technical University of Ukraine "Igor Sikorsky Kyiv Polytechnic Institute<br>(Kyiv, Ukraine).               |

| Ganna<br>Zavolodko   | Member of the Program Committee, Candidate of Technical Sciences, Associate<br>Professor of the Department "Information" of National Technical University<br>"Kharkiv Polytechnic Institute" (Kharkiv, Ukraine).                                                                        |

| Ivan Obod            | Member of the Program Committee, Member of the Organizing Committee, Doctor<br>of Technical Sciences, Professor, Professor of Department of Microprocessor<br>Technologies and Systems of Kharkiv National University of Radio Electronics<br>(Kharkiv, Ukraine).                       |

| Oleksandr<br>Vorgul  | Member of the Program Committee, Member of the Organizing Committee, Ph. D. of Technical Sciences, Assosiate Professor, Assosiate Professor of Department of Microprocessor Technologies and Systems of Kharkiv National University of Radio Electronics (Kharkiv, Ukraine)             |

| Oleg Zubkov          | Member of the Program Committee, Member of the Organizing Committee, Ph.D.,<br>Associate Professor, Assosiate Professor of Department of Microprocessor<br>Technologies and Systems of Kharkiv National University of Radio Electronics<br>(Kharkiv, Ukraine)                           |

| Liliia<br>Saikivska  | Member of the Program Committee, Member of the Organizing Committee,<br>Candidate of Technical Sciences, Assosiate Professor, Assosiate Professor of<br>Department of Microprocessor Technologies and Systems of Kharkiv National<br>University of Radio Electronics (Kharkiv, Ukraine) |

| Pavlo Galkin         | Member of the Program Committee, Senior Lecturer of Design and Operation of<br>Electronic Devices Department of Kharkiv National University of Radio Electronics<br>(Kharkiv, Ukraine)                                                                                                  |

# **Table of Contents**

| No. | Paper Title                                                                                                                                             | Page<br>No. |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.  | Features of the use of PID controllers when controlling evaporators                                                                                     | 6           |

| 2   | Oleg Zubkov, Iryna Svyd, Oleksandr Maltsev                                                                                                              | 0           |

| 2.  | Realisation of Iterative Algorithm of Six-Port Reflectometer on FPGA Using<br>Logarithm Function                                                        | 8           |

|     | Olga Zaichenko, Pavlo Galkin, Nataliia Zaichenko, Lydmila Golovkina                                                                                     |             |

| 3.  | Approaches to Designing a Wireless Sensor Network Node for IoT Solution                                                                                 | 10          |

|     | Anton Sukov, Alexey Zayanchukovsky, Vyacheslav Olizarenko, Pavlo Galkin                                                                                 |             |

| 4.  | <b>Intelligent Control and Monitoring Module for Uninterruptible Power Supply System</b><br><i>Andriy Palamar</i>                                       | 12          |

| 5.  | <b>Teaching microcontrollers and FPGAs in Quarantine from Coronavirus: Challenges</b>                                                                   | 14          |

| 0.  | and Prospects                                                                                                                                           |             |

|     | Oleksandr Vorgul, Iryna Svyd, Oleg Zubkov, Valerii Semenets                                                                                             |             |

| 6.  | Creation Features of Devices for Testing Nasal Breathing                                                                                                | 18          |

|     | Yana Nosova, Maksym Tymkovych, Sofia Khudaieva, Ibrahim Younouss Abdelhamid, Oleg                                                                       |             |

|     | Avrunin, Birgit Glasmacher                                                                                                                              |             |

| 7.  | Remote Debugging of Embedded Systems in STM32CubeMonitor                                                                                                | 22          |

|     | Oleksandr Velihorskyi, Ihor Nesterov, Maksym Khomenko                                                                                                   |             |

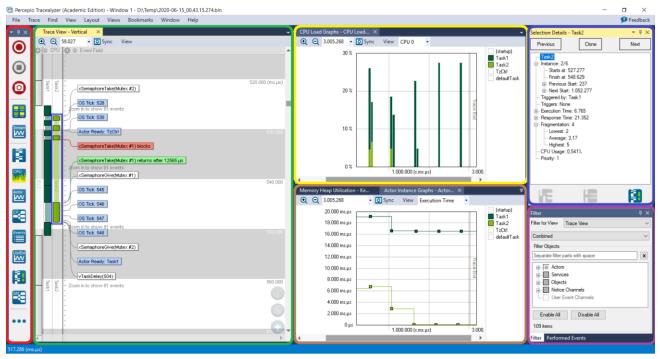

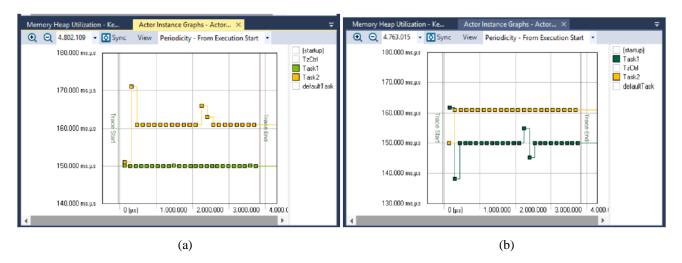

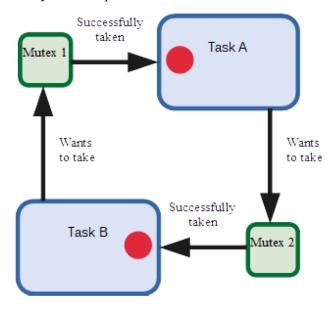

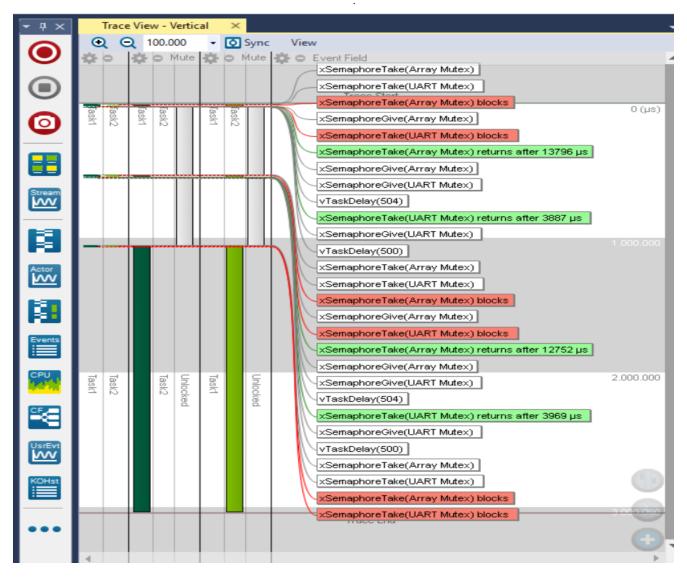

| 8.  | The Use of Percepio Tracealyzer for the Development of FreeRTOS-based                                                                                   | 26          |

|     | Applications                                                                                                                                            |             |

| 0   | Maksym Khomenko, Oleksandr Velihorskyi<br>Mathada of Organizing Communication Potwar Microsontucllors in the System of                                  | 20          |

| 9.  | Methods of Organizing Communication Between Microcontrollers in the System of<br>Monitoring Energy Consumption                                          | 30          |

|     | Sergiy Novoselov, Oksana Sychova                                                                                                                        |             |

| 10. | Using Remote Hardware Education Kit to Study Electronics Courses                                                                                        | 34          |

| 101 | Sergii V. Afanasiev, Nikita S. Poberezkyi, Sergey A. Ivanets                                                                                            | 0.          |

| 11. | Fuzzy Logic Custom Instruction Set for NIOS II Processor                                                                                                | 36          |

|     | Sergey A. Ivanets, Artem P. Fesenko, Oleksandr M. Fesiuk                                                                                                |             |

| 12. | Application of Software Signal Filtering in an Ultrasonic Rangefinder                                                                                   | 39          |

|     | Artem Khromenko, Liliia Saikivska                                                                                                                       |             |

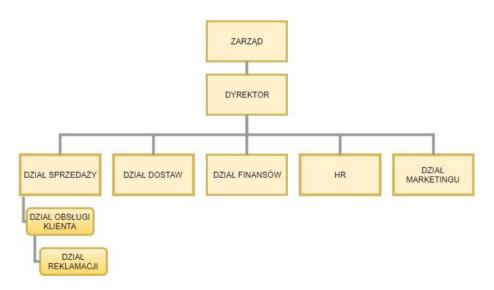

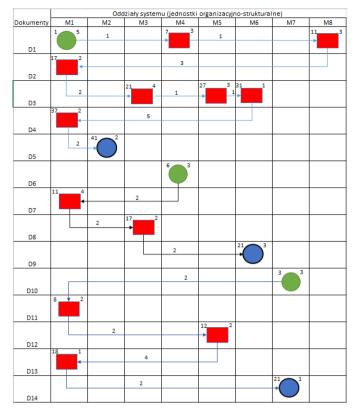

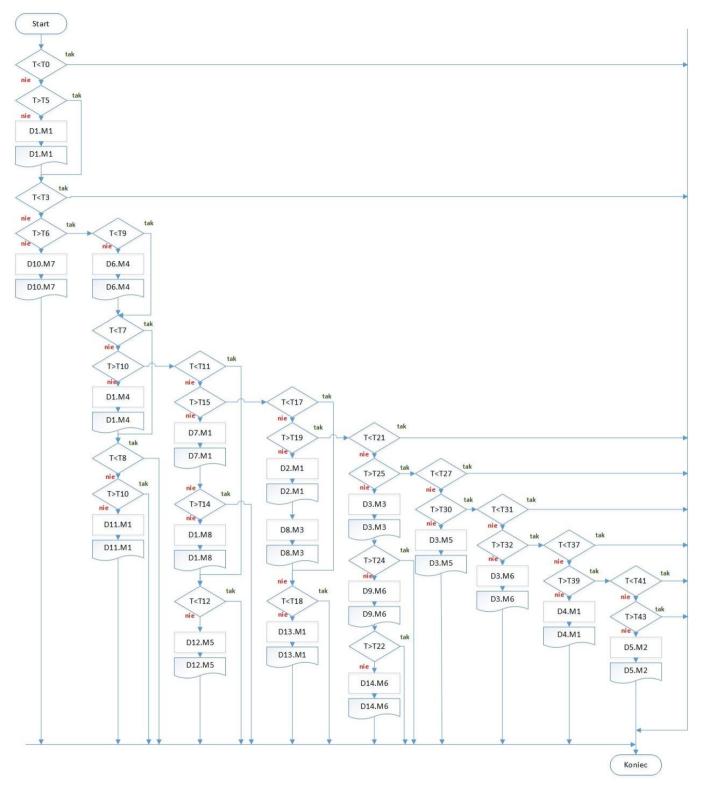

| 13. | Processes Analysis of Networks Management Systems                                                                                                       | 41          |

|     | Lubomyr Petryshyn, Wioleta Cieslik, Mykhailo Petryshyn                                                                                                  |             |

| 14. | Visualization Modeling of Networks Management Systems                                                                                                   | 45          |

| 15  | Lubomyr Petryshyn, Wioleta Cieslik, Mykhailo Petryshyn<br>Dictores Training of Higher Education Specialists Using Virtual Presence                      | 50          |

| 15. | Distance Training of Higher Education Specialists Using Virtual Presence Technologies                                                                   | 50          |

|     | Valerii Semenets, Oleg Avrunin, Tatyana Nosova, Evgen Chuguy, Yana Nosova,                                                                              |             |

|     | Oleksandr Gryshkov                                                                                                                                      |             |

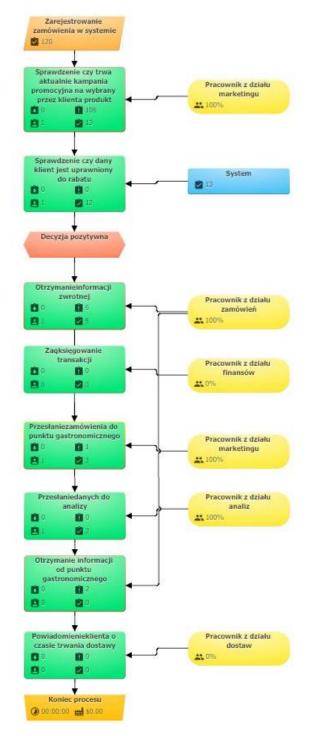

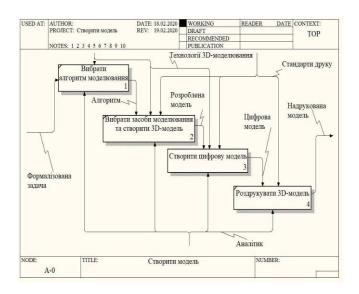

| 16. | 3D Printing in Online Education                                                                                                                         | 53          |

|     | Hanna Zavolodko, Nataliia Haidar                                                                                                                        |             |

| 17. | Special Features of the Educational Component "Design of Devices on                                                                                     | 55          |

|     | Microcontrollers and FPGA"                                                                                                                              |             |

|     | Iryna Svyd, Oleksandr Vorgul, Valerii Semenets, Oleg Zubkov, Valeriia Chumak,                                                                           |             |

| 10  | Natalia Boiko                                                                                                                                           | <b>F</b> 0  |

| 18. | <b>Literacy is an Important Factor in Professional Training of Modern Specialist</b><br><i>Viktoriia Tsyhanenko, Alla Serhiieva, Nataliia Ochkurova</i> | 58          |

# Features of the use of PID controllers when controlling evaporators

Oleg Zubkov ORCID 0000-0002-8528-6540 Department of Microprocessor Technologies and Systems Kharkiv National University of Radio Electronics Kharkiv, Ukraine oleh.zubkov@nure.ua Iryna Svyd ORCID 0000-0002-4635-6542 Department of Microprocessor Technologies and Systems Kharkiv National University of Radio Electronics Kharkiv, Ukraine iryna.svyd@nure.ua

*Abstract*—In the work, the features of the use of PID regulators for controlling evaporators are theoretically and experimentally analyzed, an algorithm for controlling the heating element of the evaporator is developed, and practical recommendations are given for choosing the parameters of the PID controller.

Keywords—PID controller, evaporator, microcontroller, algorithm, vapor

# I. INTRODUCTION

In many automated control systems for technological processes in production, boiler equipment, electric motor control systems, proportional-integral-differential controllers (PIDs) are used. With their help, a constant value of any technological parameter is maintained. For example, a constant value of the temperature of the heat carrier in heating or cooling systems. The regulation problem in modern control systems is solved by microcontrollers in combination with measuring sensors and power modules. The theoretical foundations of the operation of classical PID controllers and their settings have been studied and described in many literature sources [1-4]. However, there is a specific group of control devices for which it is necessary to modernize the algorithms of the PID regulators and their mathematical description. These are vaporizers. In such devices, the process of liquid boiling takes place, in which all the energy transferred from the heating element to the evaporator is used not to increase the temperature of the liquid, but to transfer the liquid to vapor [5]. In evaporators, the PID regulator must maintain a fixed value of the volume of steam generated per unit of time. At the same time, when the PID controller is turned on, its reaching the operating mode is complicated by the fact that the thermodynamic processes in the evaporator before boiling and during boiling are different. These scientific studies were devoted to solving these problems, which are relevant for automated control systems. The solution of these main problems is inextricably linked with a number of aspects of an applied nature: the type of measurements - direct or indirect, the location of the measuring sensors, the choice of the measurement period and the correction period for the control action. Therefore, the purpose of the research was to develop an evaporator control algorithm and form recommendations for the selection of PID controller parameters.

Oleksandr Maltsev 42 ORCID 0000-0003-1520-9280 or Department of Microprocessor Technologies and Systems Radio Kharkiv National University of Radio Electronics Kharkiv, Ukraine aleksandr.maltsev@nure.ua

### II. THEORETICAL PART

The principle of operation of the PID controller is that based on the measurement result of the main output parameter of the controlled system, the deviation of the current value from the required value is calculated and the value of the corrective action on the system is calculated [1, 3]

$$u(t) = P + I + D = K_p e(t) + K_i \int_{0}^{\tau} e(t) dt + K_d \frac{de}{dt}$$

(1)

where P is proportional component; I is integral component; D is differential component; e(t) is current error; Kp is proportional factor; Ki is integral coefficient; Kd is differential coefficient.

For evaporators with direct measurements, the main output parameter is the amount of steam generated. However, steam flow meters are very expensive devices with high measurement errors and specific measurements for various types of steam (water, alcohol, etc.). Therefore, when controlling the majority of modern evaporators, indirect measurements of vaporization are used through the temperature of the heating elements of the evaporator. Temperature is directly related to the amount of energy transferred to the evaporator and, accordingly, to the amount of steam generated.

Formula (1) is a continuous form of PID controller representation, which requires conversion to a discrete form for implementation on a microcontroller [2].

$$u(k) = K_p \left\{ \Delta x(k) + \frac{T_0}{T_{\text{int}}} \sum_{i=0}^k \Delta x(i-1) + \frac{T_d}{T_0} \left[ \Delta x(k) - \Delta x(k-1) \right] \right\},$$

(2)

where k is discrete moment in time  $(kT_0)$ ;  $T_{int}$  is constant of integration;  $T_d$  is differentiation constant;  $T_0$  is sampling period.

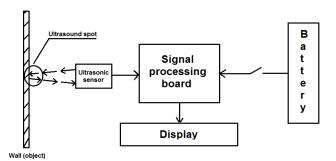

### III. EQUIPMENT OF THE EXPERIMENTAL SYSTEM

As heating elements of the evaporation system, 2 kW electric heaters with triac control were used. Therefore, the PID regulator provided control of the electrical power transmitted to the load. Thermal resistances of the Pt1000 type were used to measure the temperature. In the board of the controller for controlling the triac, a circuit for detecting the zeros of the mains voltage is implemented, which made it possible to implement two main methods of controlling the triac during research: passing a part of the half-cycle of the mains voltage into the load or passing one of the set of half-periods. The controllers of the STM32F1 and STM32F4 series were chosen as control controllers.

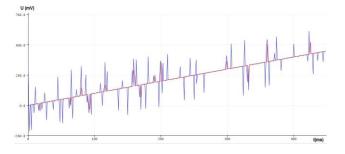

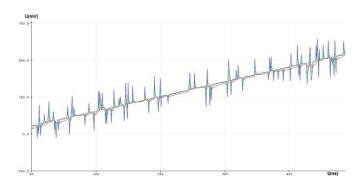

### IV. STUDY RESULTS AND PRACTICE RECOMMENDATIONS FOR EVAPORATOR CONTROL SYSTEMS

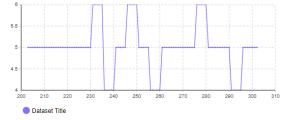

The software implementation of the standard PID controller operation algorithm according to (2) showed that the process of turning on the system is significantly extended in time in comparison with the calculation results, and overshoot is also observed in the control system. This is due to the transition from heating to boiling. To eliminate these effects at the initial stage of inclusion in the algorithm, a forced mode is introduced. In this mode, the power of the heating elements is maintained at a maximum until a predetermined temperature threshold is reached, the value of which can be either less than the operating value or higher. After that, the PID controller is turned on. However, at this moment the value of the integral component is equal to 0, since the integration is not performed from the moment the system is turned on. Therefore, the parameter of the initial value of the integral component is introduced, which makes it possible to compensate the accumulated value from the moment the system is turned on. The use of the forced mode ensured a quick activation of the system and the absence of fluctuations in the control system. Experimental studies have also shown that when the user gives commands to reduce the amount of steam per unit of time, the response value of the PID controller can drop to 0. This can lead to the termination of boiling, which is unacceptable for the evaporator. Therefore, a limitation was introduced on the minimum value of the control action of the PID controller.

Taking into account the proposed improvements, expression (2) was transformed to the form

$$u(k) = \begin{cases} u_{\max}, \ i < k_{START} \\ u_{\min}, \ u(k) < u_{\min}, \ i > = k_{START} \\ K_p \left( \Delta x(k) + I_{START} + \frac{T_0}{T_{\inf}} \sum_{i = k_{START}}^k \Delta x(i-1) + , \\ + \frac{T_d}{T_0} [\Delta x(k) - \Delta x(k-1)] \right) \end{cases}$$

(3)

where  $u_{\text{max}}$  the maximum power value of the evaporator heating elements;  $u_{\text{min}}$  the minimum value of the power supplied to the heating element in the operating mode of the evaporator;  $k_{\text{START}}$  moment of time from switching on to switching off the forced mode;  $I_{\text{START}}$  the initial value of the integral component at the moment of switching off the forced mode.

The optimal location for the temperature sensor is the outer surface of the heating element, since this provides a wide dynamic range of temperature measurements for the heating element. In the research stand, it reached 60°C.

Since the developed control algorithm was implemented on modern 32-bit microcontrollers with an ARM core, all calculations in the PID controller were performed with floating point. For STM32F1 microcontrollers, the calculation time does not exceed 80  $\mu$ s, and for STM32F4 microcontrollers, no more than 1  $\mu$ s due to the hardware DSP block. Thus, even the cheap STM32 microcontroller series can implement one or more PID controllers.

#### V. CONCLUSION

According to the classical theory of PID controllers, the differential component is influenced by noise, which manifests itself as fluctuations in the temperature measurements of the heating elements over time. With a normal distribution of measurement errors, the standard deviation decreases in proportion to the square root of the number of measurements. Experimental studies have shown that in order to achieve temperature fluctuations of no more than  $\pm 0,07^{\circ}C$  smoothing should be implemented over a time interval of 1 s for 100 measurements. Such a time interval was chosen based on the provision of 100 discrete power levels of the evaporator heating elements, which correspond to 100 half-periods of the mains voltage for 1 s. A further increase in the value of this parameter is impractical, since a delay in the response of the PID controller to a change in the temperature of the heating elements begins to appear.

Experimental verification of the developed algorithm on a test bench has shown its efficiency and stability.

#### REFERENCES

- C.B. Kadua, C.Y. Patil. Design and Implementation of Stable PID Controller for Interacting Level Control System. Procedia Computer Science. Vol. 79, 2016, Pages 737-746.

- [2] J. Farshad Merrikh-Bayat, Nafiseh Mirebrahimi, and Mohammad Reza Khalil. Discrete-time fractional-order PID controller: Definition, tuning, digital realization and some applications International Journal of Control, Automation, and Systems, 2015 Vol. 13(1), pp. 81-90.

- [3] V. Chopra, S. K. Singla, and L. Dewan, "Comparative analysis of tuning a PID controller using intelligent methods," Acta Polytechnica Hungarica, vol. 11, no. 8, pp. 235–249, 2014.

- [4] Semenets V. V., Kratts Dzh., Nevlyudov I. Sh., Palagin V. A. Tekhnologiya mezhsoedinenii elektronnoi apparatury. Ucheb. dlya vuzov. Khar'kov: «SMIT», 2005.

- [5] Bambang Dwi Argo, Yusuf Hendrawan, Dimas Firmanda Al Riza, Anung Nugroho Jaya Laksono. Optimization of PID Controller Parameters on Flow Rate Control System Using Multiple Effect Evaporator Particle Swarm Optimization. International journal on advanced science engineering information technologies. Vol.5 (2015) No. 2. pp. 6-12.

MC&FPGA-2020

# Realisation of Iterative Algorithm of Six-Port Reflectometer on FPGA Using Logarithm Function

Olga Zaichenko ORCID 0000-0003-4936-2785 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine olha.zaichenko@nure.ua

Nataliia Zaichenko ORCID 0000-0001-9798-7136 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine nataliia.zaichenko@nure.ua

Abstract—The six-port reflectometer is an universal measurement device of microwave range for signal power and tract termination reflection coefficient definition. The definition of such tract and termination parameters is made by sensor signal processing. As processing algorithm can be used least squares estimation. The advantages of least squares estimation is accuracy. The condition of its use is redundandant sensor number. The least squares estimation feature is invers matrix computation. As to FPGA realisation of algorithm there are problems connected to matrix inversion. So the report is devoted to attempt to simplify six-port reflectometer sensor signal processing and to avoid inverse matrix computation.

Keywords—six-port reflectometer, processing algorithm, least squares estimation, logarithm

#### I. INTRODUCTION

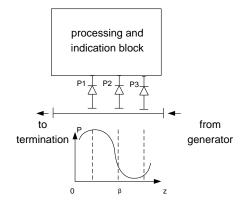

The six-port reflectometer [1, 4, 5] consists of waveguide section and processing and indication block. The processing and indication block can be realized on FPGA.

Fig. 1. The six-port reflectometer with three sensors.

The waveguide section located between generator and termination. Due to electromagnetic wave reflection from termination inside waveguide section is standing wave. There are sensors along standing wave in the waveguide. The Pavlo Galkin ORCID 0000-0002-0558-6448 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine pavlo.halkin@nure.ua

Lydmila Golovkina ORCID 0000-0001-5929-3256 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine liudmyla.holovkina@nure.ua

sensors signals proportional to intensity of electromagnetic wave in their position. To extract information about signal power and reflection coefficient modulus ana phase it is necessary process sensor signals by definite algorithm. As mathematical model of ideal six-port reflectometer is system of linear equation, where each equation corresponds to one sensor, to get algorithm is necessary to solve the system of linear equation through inverse matrix, unlike non ideal sensor processing. Processing of non ideal sensors demand more complicated algorithm, for example, least squares estimation.

The problem of this research is contradiction between accounting an uncertainity of measurement by mean of complication processing methods and realization of computation methods on FPGA, using hardware description language VHDL, where computation mathematics should be implemented by hardware units.

# II. ITERATIVE ALGORITHM OF SIX-PORT REFLECTOMETER

Lets sensor number exceed unknown intermediate variable number. As mathematical model we have redundant system of linear equation [1]. The solution of such system through the least squares estimation is

$$\begin{bmatrix} b \end{bmatrix} = \left( \begin{bmatrix} A \end{bmatrix}^T \begin{bmatrix} A \end{bmatrix} \right)^{-1} \begin{bmatrix} P \end{bmatrix}.$$

(1)

To avoide inverse matrix calculation lets apply iterative Seidel algorithm

$$b_{0} = \frac{1}{f_{11}} \{ a_{11}p_{1} + a_{21}p_{2} + a_{31}p_{3} + a_{41}p_{4} - (f_{12}b_{1} + f_{13}b_{2}) \}$$

$$b_{1} = \frac{1}{f_{22}} \{ a_{12}p_{1} + a_{22}p_{2} + a_{32}p_{3} + a_{42}p_{4} - (f_{21}b_{0} + f_{23}b_{2}) \} (2)$$

$$b_{2} = \frac{1}{f_{33}} \{ a_{13}p_{1} + a_{23}p_{2} + a_{33}p_{3} + a_{43}p_{4} - (f_{13}b_{0} + f_{32}b_{1}) \}$$

where system matrix is

$$[A] = \begin{pmatrix} 1 & \cos\phi & \sin\phi \\ 1 & 1 & 0 \\ 1 & \cos\phi & -\sin\phi \\ \dots & \dots & \dots \\ 1 & \cos n\phi & -\sin n\phi \end{pmatrix},$$

(3)

matrix column of sensor signals is

$$[P] = (P_1 \ P_2 ... P_n)^T.$$

(4)

Intermediate variable is

$$\begin{bmatrix} b \end{bmatrix} = \begin{pmatrix} b_1 b_2 \dots b_n \end{pmatrix}^T.$$

Definition for intermediate variables is

$$b_0 = P_{inc} (1 + \Gamma^2),$$

$$b_1 = \Gamma P_{inc} \cos \phi,$$

$$b_2 = \Gamma P_{inc} \sin \phi,$$

(6)

where  $\Gamma$  is reflection coefficient modulus,  $\varphi$  is reflection coefficient phase,  $\theta$  is phase distance between neighbouring sensors,  $P_{inc}$  is incident power. For expression (2) also necessary expression. They are calculated from information Fisher matrix

$$\begin{split} f_{11} &= a_{11}^2 + a_{21}^2 + a_{31}^2 + a_{41}^2 \\ f_{12} &= a_{11}a_{12} + a_{21}a_{22} + a_{31}a_{32} + a_{41}a_{42} \\ f_{13} &= a_{11}a_{13} + a_{21}a_{23} + a_{31}a_{33} + a_{41}a_{43} \\ f_{21} &= a_{11}a_{12} + a_{21}a_{22} + a_{31}a_{32} + a_{41}a_{42} \\ f_{22} &= a_{12}^2 + a_{22}^2 + a_{32}^2 + a_{42}^2 \\ f_{23} &= a_{12}a_{13} + a_{22}a_{23} + a_{32}a_{33} + a_{42}a_{43} \\ f_{31} &= a_{11}a_{13} + a_{21}a_{23} + a_{31}a_{33} + a_{41}a_{43} \\ f_{32} &= a_{12}a_{13} + a_{22}a_{23} + a_{32}a_{33} + a_{42}a_{43} \\ f_{33} &= a_{13}^2 + a_{23}^2 + a_{33}^2 + a_{43}^2 \end{split}$$

Analysis of expression shows that on VHDL should be realised summation, multiplication and exponentiation.

#### III. HARDWARE IMPLEMENTATION

In the paper [2],an FPGA-based single precision floating point hybrid iterative architecture for solving a linear system of equations is proposed. The whole design has been implemented in Verilog HDL, having Virtex 7 XCV2000T as targeted device. The design optimizations include using modified high-speed radix 4 multiplier and optimized highspeed 2's complementer. The Radix-4 Booth Encoded multiplier is the most speed efficient and area efficient among other higher radix Booth Encoded multipliers. The partial products required for computation are significantly reduced compared to the traditional multipliers. These partial products are added using a Dadda tree structure and the final summation is carried out using a Koggestone adder.

This approach has many advantage and it is verified, but we propose an idea of alternative solution. The idea is borrow from operational amplifier. The idea is instead of calculation of product there is made calcultion of sum of multipicant logarithm.

The logariphm calculation is performed by such methods as: 1) recursive algorithm for calculating the logarithm; 2) the comparison method to 2; 3) discrete logarithm; 4) logariphm ruler, 5) lookup table. The elements of this approach are contained in [3].

The second method, comparison to 2 method algorithm is: 1. The number is compared to 2; 2. If greater than 2: then divide it by 2 and go to 1 step; 3. if less than 2, but more than 1: then remember the number of divisions by 2 (this there will be an integer part of the logarithm); 4. output the result. Advantages: 1) Possibility of implementation on logic elements; 2) Speed of calculations. Disadvantages:1) Calculates only an integer, without a remainder.

### IV. CONCLUSION

There was proposed new iterative method of six-port reflectometer sensor signal processing. It is based on least squares estimation iterative calculation by Seidel method for example. It allows to avoid inverse matrix calculation and leaves only calculation of sum and product. There was worked out procedura for computation.

Implementation of such algorithm on FPGA is considered from hardware point of view. The inherited from operational amplifiers logarithmic transformation, i.e. instead of calculation of product there is made calcultion of sum of multipicant logarithm lays in its foundation.

#### REFERENCES

- O. Zaichenko, P.Galkin, N. Zaichenko, and M. Miroshnyk, "Six-port Reflectometer with Kalman Filter Processing of Sensor Signals,". IEEE 15th International Conference on Advanced Trends in Radioelectronics, Telecommunications and Computer Engineering (TCSET), pp. 55-58, February2020.

- [2] R. Joshi, A. Raghuvanshi, Y. Gilhotra, S. Sharma, S. Sharma, P. Dalmia, and N. Pandey, "An FPGA based floating point Gauss-Seidel iterative solver," 14th IEEE India Council International Conference (INDICON), pp. 1-6, December2017.

- [3] Usirkov K. V. "Analysis of mathematical operation realization on FPGA," Master dissertation, South-Ural state university, 2016, 48 p.

- [4] O. Zaichenko, M. Miroshnyk and P. Galkin, "Signal Flow Graph for Optimizing of Mutual Sensors Reflection in the Multiprobe Microwave Multimeter," 2019 IEEE 2nd Ukraine Conference on Electrical and Computer Engineering (UKRCON), Lviv, Ukraine, 2019, pp. 200-203, doi: 10.1109/UKRCON.2019.8879925.

- [5] O. Zaichenko, P. Galkin and M. Miroshnyk, "Model and Algorithms for Microwave Mutiport Receiver," 2019 IEEE International Scientific-Practical Conference Problems of Infocommunications, Science and Technology (PIC S&T), Kyiv, Ukraine, 2019, pp. 1-4, doi: 10.1109/PICST47496.2019.9061275.

# Approaches to Designing a Wireless Sensor Network Node for IoT Solution

Anton Sukov

dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine anton.sukov@nure.ua

Vyacheslav Olizarenko

dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine viacheslav.olizarenko@nure.ua

Abstract—The object of the research is the hardware component for building a test platform for wireless sensor networks. The aim of the work is to develop a software and hardware test platform for wireless sensor networks. As a result of the analysis, the node structures, wireless sensor network modules, CC2530 peripherals were analyzed. A module based on the CC2530 PA was chosen as the hardware. Given to optimize the structure of the node for as one of approach to designing a wireless sensor network node. Also given report about difference in approach to designing nodes and uses areas. All developments will receive life in the educational process of the department. Sample production is already underway.

Keywords—approach, CC2530, software and hardware test platform, node, wireless sensor network

### I. INTRODUCTION

The Wireless sensor networks (WSN) systems have a lot of problems like security, energy consumption, heterogeneity and other disadvantages that need be solved [1]. Therefore, it is quite difficult to design a sensor network node so that it satisfies the necessary criteria for optimality. If such a node is also used for testing and training, then additional requirements for the construction will be propose to, for example, as in articles of designing microprocessor systems [2] or embedded control systems [3]. Energy monitoring [4] is a key factor for the successful prolongation of life times each nodes in wireless sensor network, for examples reducing the power consumption of nodes [5]. Therefore, can set the task to optimize the structure of the node for as one of approach to designing a wireless sensor network node.

The purpose of the work is to develop a software and hardware test platform for the Internet of Things.

The first part the development of a test IoT layout, namely, a communication module based on the CC2538 radio transceiver.

The second part development of a test IoT layout. Communication module based on the CC2530 radio transceiver.

Alexey Zayanchukovsky

dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine oleksii.zaianchukovskyi@nure.ua

Pavlo Galkin ORCID 0000-0002-0558-6448 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine pavlo.halkin@nure.ua

The third part is development of a test IoT layout, namely, a communication module based on the ESP8266 radio transceiver.

# II. CC2530 NODE FOR IOT

The CC2530 contains many peripherals that provide everything to develop various applications. The debugging interface uses I/O ports P21 (data) and P22 (synchronization) in debug mode. In this case, in the debug mode, the other 19 ports pins can be active, which gives a great opportunity to debug the module, while at the same time it can be connected to quite a few different devices. In other cases, the ports for debugging can work in the normal GPIO mode. In general, the debugging interface allows you to track all processes that occur in the module when it is in an active state (user program execution), and also to change the parameters of these processes (for example, values in registers) and in real time to observe changes in the work of the module.

As a result of the analysis, the node structures, wireless sensor network modules, peripherals CC2530 were analyzed. A module based on CC2530 PA was chosen as the hardware. Elements such as:

- LEDs ;

- push buttons;

- photoresistor;

- humidity sensor;

- ultrasonic sensor;

- exits to the outer periphery.

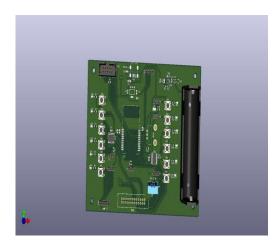

Fig. 1. Developed PCB board base on CC2530.

# III. CC2538 NODE FOR IOT

The CC2538xFnn is the ideal wireless microcontroller System-on-Chip (SoC) for high-performance ZigBee applications. The device combines a powerful ARM Cortex-M3-based MCU system with up to 32KB onchip RAM and up to 512KB on-chip flash with a robust IEEE 802.15.4 radio. This enables the device to handle complex network stacks with security, demanding applications, and over-theair download.

As a result of the analysis, the node structures, wireless sensor network modules, CC2538 peripherals were analyzed. A module based on the CC2538 was chosen as the hardware. As elements of the periphery, the following elements were chosen:

- LEDs;

- push buttons;

- Temperature, humidity and pressure sensor in the one case;

- Buzzer;

- hall sensor;

- lighting sensor;

- voltage divider with adjustable resistor.

A contact switch is selected to switch between the peripheral elements, and electrical switch for switching between external and internal peripheral (Fig. 2).

# IV. ESP8266 NODE FOR IOT

The ESP8266 is a low-cost Wi-Fi microchip, with a full TCP/IP stack and microcontroller capability, produced by Espressif Systems in Shanghai, China.

Proposed developed PCB board base on ESP8266 shown on Fig.3.

### V. CONCLUSION

The topic of the modern concept of IoT and the possibilities of the ZigBee protocol were considered. Similar devices were considered. The selected module and its

capabilities were considered. The model is developed, its separate possibilities and components are considered.

Fig. 2. Developed PCB board base on CC2538.

Fig. 3. Developed PCB board base on ESP8266.

### REFERENCES

- [1] C. Alvarado, F. Bosquez, Palacios and L. Córdoba, "Low-energy Adaptive Clustering Hierarchy protocol and optimal number of cluster head algorithm in a randomized wireless sensor network deployment," 2017 International Conference on Electrical, Electronics, Communication, Computer, and Optimization Techniques (ICEECCOT), Mysuru, 2017, pp. 1-4. doi: 10.1109/ICEECCOT.2017.8284632.

- [2] V. Semenets, "Technical aspects for development laboratory base for learning FPGA and microcontroller systems," 2009 10th International Conference - The Experience of Designing and Application of CAD Systems in Microelectronics, Lviv-Polyana, 2009, pp. 145-145.

- [3] P. Galkin, "Razrabotka laboratornogo kompleksa po izucheniyu vstraivaemyih sistem upravleniya i promyishlennoy avtomatizatsii [Development of a laboratory complex for the study of embedded control systems and industrial automation]," Materials of the 21st International Youth Forum "Radio Electronics and Youth in the 21st Century", April 25-27, 2017 Conference "Automated systems and computerized technologies of radio-electronic instrument-making", Kharkiv, KNURE, vol. 2, P.94-95. (In Russian).

- [4] P.V. Galkin. "Analiz energopotrebleniya uzlov besprovodnih sensornih setei [Analysis of power consumption of nodes of wireless sensor networks]," ScienceRise, no.2 pp 55-61, 2014. (In Russian).

- [5] P. Galkin, "Model of Reducing the Power Consumption for Node of Wireless Sensor Network in Embedded Control Systems," 2018 International Scientific-Practical Conference Problems of Infocommunications. Science and Technology (PIC S&T), Kharkiv, Ukraine, 2018, pp. 252-256. doi: 10.1109/INFOCOMMST.2018.8631891.

II International Scientific and Practical Conference Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs

MC&FPGA-2020

11

# Intelligent Control and Monitoring Module for Uninterruptible Power Supply System

Andriy Palamar ORCID 0000-0003-2162-9011 Computer Systems and Networks Department Ternopil Ivan Puluj National Technical University Ternopil, Ukraine palamar.andrij@gmail.com

*Abstract*—This paper proposes an intelligent control and monitoring module for industrial uninterruptible power supply systems. The structure scheme of the module based on the parallel connected of two microcontrollers with ARM architecture is designed. The software for the module is developed and implemented.

Keywords—control system, monitoring, microcontroller, uninterruptible power supply.

### I. INTRODUCTION

Industrial uninterruptible power supply (UPS) systems are widely used in order to ensure high quality power supply and protection of electronic equipment from failure. One of the most important components of modern UPS is a computer information and measurement system [1].

In most UPS, the core of such system is a microprocessor or microcontroller that performs all of the monitoring and control functions. Quite often, UPS is used to provide guaranteed power to remote objects to which the operator does not have constant access, so there is a requirement for remote monitoring of the device and its electrical parameters.

In the software and hardware complex, which was developed by the author [2, 3], the process of data transfer to a PC for remote monitoring is implemented using the Ethernet protocol, which requires significant hardware and software resources of the microcontroller. On the other hand, the process of battery charge management also requires significant computing power, as it requires operations of analog-to-digital conversion of electrical signals, and rapid response to changes in measured data depending on the control mode.

The combination of these tasks creates a significant load on the computing power of the microcontroller, which in turn reduces the response rate to changes in the electrical parameters of the battery, which is critical during transients during battery charging. To solve this problem, this paper proposes design and implementation of a two-core information and measurement control system for an uninterruptible power supply system, which implements the principle of parallelization of tasks.

The purpose of the work is to increase the reliability and efficiency of the industrial UPS control module by using parallel operation of two 32-bit microcontrollers.

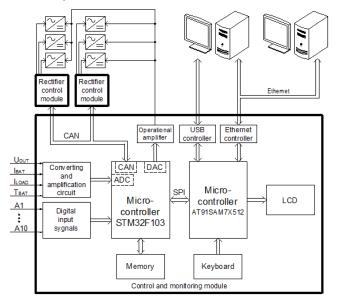

### II. THE STRUCTURE OF THE MODULE

The UPS control module implements functions of electric parameters measurement and battery charge management process, check a condition of alarm signals, provides an opportunity of archiving of the measured data, carries out transfer of the received information to the personal computer.

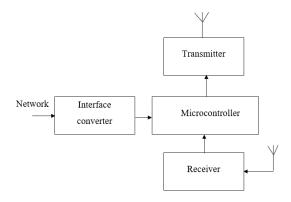

The schematic block diagram of the control and monitoring module for uninterruptible power supply system is shown in Fig. 1. The structure of the module contains:

- two microcontrollers (STM32F103 and AT91SAM7X512);

- conversion and amplification circuit for receiving input analog signals;

- circuit that is responsible for receiving digital input signals;

- non-volatile memory chip for storing received data;

- USB and Ethernet controllers for PC connection;

- keyboard and LCD for user interaction.

Fig. 1. Block diagram of the control and monitoring module for uninterruptible power supply system.

Two 32-bit microcontrollers based on the ARM architecture provide basic control and monitoring functions of the UPS. The STM32F103 microcontroller contains builtin 16-channel 12-bit analog-to-digital converter (ADC) and two-channel digital-to-analog converter (DAC). It is responsible for performing tasks that require frequent checking of the system status and measuring its electrical parameters by using ADC. This microcontroller provides fast response to their change by generating an analog control signal for UPS rectifier modules using DAC. In addition, this microcontroller performs the function of controlling the operating modes of the USP such as battery charge process, residual capacity testing, etc.

The AT91SAM7X512 microcontroller with integrated Ethernet, CAN and USB interfaces is responsible to perform tasks that are not time-critical. For example, displaying of the measured data on the LCD display, reading the keyboard, transferring the information to the server for its storage in database and further processing. Serial peripheral interface (SPI) is used to provide fast and reliable data exchange process between these microcontrollers.

After the conversion and amplification, voltage, currents, and temperature signals are measured by using inner analogto-digital converter of the STM32F103 microcontroller. All deviations of the measured data from the normal values, alarms as well as time of an event are stored in a non-volatile memory.

The received data are visualized on the LCD on the front of the module. Electrical parameters of the system can be set or changed using the keyboard with four buttons. Digital signals of the UPS status are being read periodically by using the input output ports of the microcontroller. Real time clock is used to keep track of the current time.

A prototype of the designed control and monitoring module is illustrated in Fig. 2.

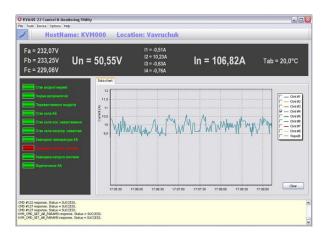

Fig. 2. A prototype of the control and monitoring module for an uninterruptible power supply.

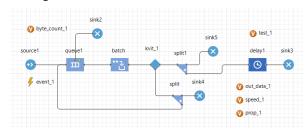

# III. THE SOFTWARE OF THE MODULE

The software of the control and monitoring system comprises of two parts. The first one is firmware for the microcontrollers. It is written by using C programming language. The second part of the software is a computer monitoring application – graphical user interface (Fig. 3).

Fig. 3. Graphical user interface of UPS monitoring system for PC.

The main program of the microcontrollers includes the following subroutines: system initialization; data collection and processing; monitoring and display unit; control unit; data transfer unit.

The function of data collection and processing unit is to provide digitizing of the measured data and their previous processing. Information required to be collected includes: output voltage; battery current; load current; battery temperature. These data are used for management purposes of the control system.

The monitoring and display unit is designed to visualize the measured information on the LCD in a real-time and to provide access to archived data. Furthermore, it allows one to set and to modify parameters of the system.

Data transfer unit is responsible for transmitting the information to the computer through the Ethernet or USB interface. The amount of data to be transferred includes: the measured information, electrical parameters of the system, and the archived data from the memory of the module.

# IV. CONCLUSIONS

In this paper an intelligent control and monitoring module for UPS system was designed and implemented. The results of experimental tests of the developed module shows that the technology of parallelization of tasks by using two microcontroller allows to increase the reliability and efficiency of the control system for an uninterruptible power supply.

#### REFERENCES

- T. Addabbo, A. Fort, M. Mugnaini, V. Vignoli. "Distributed UPS control systems reliability analysis," Measurement, 2017, Vol. 110, pp. 275–283. doi: 10.1016/j.measurement.2017.06.021

- [2] A. Palamar, M. Karpinskyy. "Control of an uninterruptible power supply in a DC microgrid system," 10th International Symposium Symposium "Topical Problems in the Field of Electrical and Power Engineering" and "Doctoral School of Energy and Geotechnology II", Pärnu, Estonia. 2011, pp. 80–84.

- [3] A. Palamar, M. Karpinskyy, V. Vodovozov. "Design and implementation of a digital control and monitoring system for an AC/DC UPS," 7th International Conference-Workshop "Compatibility and Power Electronics" CPE 2011, Tallinn, Estonia. 2011, pp. 173–177. doi: 10.1109/CPE.2011.5942227

# Teaching microcontrollers and FPGAs in Quarantine from Coronavirus: Challenges and Prospects

Oleksandr Vorgul ORCID 0000-0002-7659-8796 Department of Microprocessor Technologies and Systems Kharkiv National University of Radio Electronics Kharkiv, Ukraine oleksandr.vorgul@nure.ua

Oleg Zubkov ORCID 0000-0002-8528-6540 Department of Microprocessor Technologies and Systems Kharkiv National University of Radio Electronics Kharkiv, Ukraine oleh.zubkov@nure.ua

Abstract—Modern equipment is becoming more and more complex and education establishment must keep up with it and offer its contribution to the overall progress. The goal of this work is to find the way how to survive on self-isolation and teach microcontrollers and FPGAs. What challenges need to be overcome and what prospects may open up.

Keywords—digital signal processing; microprocessor; STM32; programmable logic integrated circuits; learning online

### I. INTRODUCTION

We were studying and teaching microcontrollers and FPGA. And suddenly a corona virus, quarantine and self-isolation. So we are self-isolated together. The bosses continued to lead the educational process in isolation from teachers, teachers teach in isolation from students, students should have an opportunity and a feedback channel.

Man is a social being, and non-verbal communication methods appeared earlier than speech. What is my point? Work in self-isolation in a trivial form can be reduced to the distribution of teaching materials, which excludes contact in the "teacher-student" system. And the channels, verbal and non-verbal, are closed. Therefore, the upbringing process is actually terminated. Furthermore, for hardware specialties, it is also important that students have, let's say, less opportunities to explore equipment on their own and gain practical experience with real equipment, not its simulation model or with just a theory. And this is not seems to be good.

Despite the fact that the teaching load during selfisolation, according to subjective feelings, is much greater than with the contact form of training, quarantine is something new, while exploring it one can get a new quality and finally improve.

### II. WHAT EXPIRIENCE CAN WE FIND IN THE INTERNET

Along with self-isolation, it became possible to visit the Coursera platform [1], to participate on the student's part in

Iryna Svyd ORCID 0000-0002-4635-6542 Department of Microprocessor Technologies and Systems Kharkiv National University of Radio Electronics Kharkiv, Ukraine iryna.svyd@nure.ua

Valerii Semenets ORCID 0000-0001-8969-2143 Department of Microprocessor Technologies and Systems Kharkiv National University of Radio Electronics Kharkiv, Ukraine valery.semenets@nure.ua

courses on our interests, to imagine what the creation of such a course in our disciplines will mean, in which direction it can be continued and for fun.

The following were selected as experimental courses:

- Digital Signal Processing from École Polytechnique Fédérale de Lausanne;

- Digital signal processing (in Russian) from the Polytechnic University, St. Petersburg;

- Hardware Description Languages for FPGA;

- Embedded Hadrware and Operation system from the University of Turku.

In each course, the platform offers:

- *A. Presentation of the course. Like video annotations and self-promotion.*

- B. The course being structurized on the weekly blocks with summing up the final results and issuing certificates.

- C. Each block contains:

- Video lectures with video text. Basically, courses on the platform are in English. The courses were not specially selected from universities in different countries, it happened unintentionally. In terms of pronunciation and understanding, the French course is distinguished by perhaps excellent English with a good writing style and the use of Python to illustrate the use of digital processing. Russian course contain a serious theoretical approach and emphasis on MATLAB. Colorado Course – in American English, contrasting with English from Lausanne – has a well-thought-out system of practice. Tasks for modeling HDL nodes are made in the ModelSim program. The simulation result is an HDL file in one of the modeling languages. The course consists of

two parts, which are the same in structure, but with slightly different presentation styles due to the fact that it is taught by different teachers. The highlight of the Colorado course is the use of a proprietary testbench file format (the student cannot make changes to this file) to validate the assignment. As a result, the verification of the correctness of the scheme is performed on the website of the course compiler using the data file generated by the testbench file.

- There is text below the video lecture. It is synced to the video if the video is running or paused using an underline. The platform provides a translation button for other languages, but it seems that this will appear in the next version.

- During video playback, it is possible to insert small questions for the listener, which stimulates the listener to pay more attention to watching the video, and not to perceive it as background noise. However, correct or incorrect answers to simple questions do not affect the overall rating.

- In addition to video, it is possible to use text materials for classes (files with examples of solved problems, pdf format, scripts with programs illustrations in python).

- After studying the above material, the student is asked to take a test. The compiler of the course has the right to decide whether to allow passing the next item (practical task). Stating the pass level of rating, if there are several tests, the compiler of the course can prohibit the transition to the next part if the previous one has not been completed. So you can build different strategies.

- During the test, you need to complete the task and enter the answer in the form of one number in the whole format, with a fixed point or in the form of a formula. Formulas are introduced in an unusual way, but you can get used to it. As with any other minor problem, entering answers in the form of arrays of numbers can cause problems for listeners. They need to be promptly answered by the course compilers, so the work here requires patience and attention from both sides.

In terms of using a platform that is essentially paid, the interest of the listener is maintained. Apparently, the moderators stimulate the creators of the courses, or competition affects the fact that the course for the student is interesting and well received. The level of the student at the entrance to the course is not checked and in order to fulfill the interestingness and perceptibility one has to choose between the fundamental nature of the course and its popularity.

If the student does not fit into the work schedule, he is offered a transfer of dates of classes. A rather high volume of rhythmic work is required from the listener. The courses, in principle, indicate the time spent in hours and minutes, which, according to the authors, are required to complete a particular task, but, of course, this is very individual. Conclusion: good idea. Either theory or hardware modeling is proposed for study. Suitable for learning languages (foreign or programming) very well, but this is not our case. When studying electronic circuits, digital or analog, simulation is used. But we need a sound training on hardware issues and it is a completely different story.

# III. HOW GOOD OUR ENVIREMENT WAS BEFORE THE CARANTINE

With an in-class, contact version of training, an educational institution has the opportunity to spend funds on the purchase of equipment and time for training personnel in order to confirm its relevance in the educational services market, where we are so amicably going. And with the interest of all parties to the process: students, teachers and employers, the listener at the exit should be ready for a smooth and comfortable transition from training to professional activity. Taking into account the realities existing before the quarantine, the experience of the teaching staff and the technical equipment of the staff makes it possible to train a technical specialist from a student [2]. However, an important component of the result is the listener's motivation, which there is still room for improvement.

# IV. WHAT FUTURE DO WE DREAM ABOUT?

Our goal is to bring back full laboratory work. Apparently, mixed learning can be a good option - contact with support of the online version, this is possible if you provide layouts for use over the network. This will require changes to the educational process. There is complete certainty here only in one thing: it will not be easier than in the contact version.

After spending nearly four months in deep online, what are our is the general first impression? As for me, I don't like the situation as it is. Let me rename what exactly.

# A. Motivation falls.

Both on the part of the student and on the part of the teachers. It needs to be somehow supported in terrible conditions (no prestige, no decent salary, few points of application of forces are visible, it is hard to see what will happen next).

# B. Teacher load has increased.

Why? But because all the plans, the most individual ones, suggest a stationary regime. Usually we plan in July and we carry out our load the whole year, and the high authorities do not throw additional task as a pleasant surprise. And even there is enough time for scientific work. But we now have a transitional regime. We pass from one stationary state to another. And if the current stationary state can somehow be described, then what will happen in the future is not clear and there are prospects in this: you can try to change something. Let's hope for the best changes in the quality learning environment.

# *C. Platforms such as Coursera - it is payable, modern and it works.*

For the instructor, this is an additional burden of mastering, course installation (both are once), update and support (both are all the time).

# D. Conducting classes online for a theoretical or praktical course.

Conducting classes online for a theoretical course, from one side, and hardware like microprocessors and FPGAs, from another side are very different. It is necessary to come up with an active part of the assignment for the student so that it is feasible and not by copypasting or rewriting.

# E. With software.

Three parts of the course. Digital processing is process modeling, STM32 microprocessors and FPGAs [5-11]:

- For digital processing, Matlab is actually the standard. In the installation of the student part of the course, especially online, you have to require students to install programs. There are free, trial, online versions of Matlab. Students balk and look for reasons to get out (here: low motivation!). Instead of Matlab, you can try Octava or Python with libraries that are free software or free. For such software, there are no fundamental problems to implement the same task as for Matlab, but the time (which is not) to enter the mode and develop a digital copy of the course increases.

- STM32. There are several options for proprietary software (free), for many platforms, for Windows, Linux and MAC OS. You can build a course based on paid software with the support of sponsors from production.

- There is no such diversity for FPGAs. Chip and evaluation board manufacturers offer large, complex software, often for a fee [3, 4]. Simulation options are available for HDL hardware description languages - VHDL and Verilog. So far we are only interested in VHDL. For this case, there exists a student version of ModelSim for Windows that also supports Verilog. As for Linux, GHDL and FreeHDL for Linux, but if you switch to Verilog, you will need to change the software. Mixed projects are problematic.

The university staff has developed a sufficient number of hardware platforms for laboratory workshops and proposed several approaches to solving the problems of remote access to laboratory equipment, presented in [5-15].

Conducting laboratory work on hardware online is a real challenge, which is currently at the stage of testing the optimal use cases.

# V. CONCLUSIONS

In the days of offline learning, the main form of education was lecture. Its support was a book (textbook and study guide) and consultations. To obtain practical skills we could use practical classes and laboratory works, qualitatively wrapped in preparation for classes by students, preparation of class time material and homework by teachers and high-quality, albeit sometimes tedious, defense of laboratory work. But practical and laboratory ones are nevertheless carried out under the guidance of a teacher, although they contain some of the student's independent work.

In the case of online classes, the lecture in the form of a file is ineffective; lecture-video, with questions-tasks during playback is much better. Information can be dosed in small portions. And leave part of the material in the reference form. A good form of lecture is a presentation with sound, in which the lecturer has the opportunity to draw explanations and graphs on the finished material. The advantage of online learning is that it is quite easy to add multimedia illustrations - video clips or sound effects.

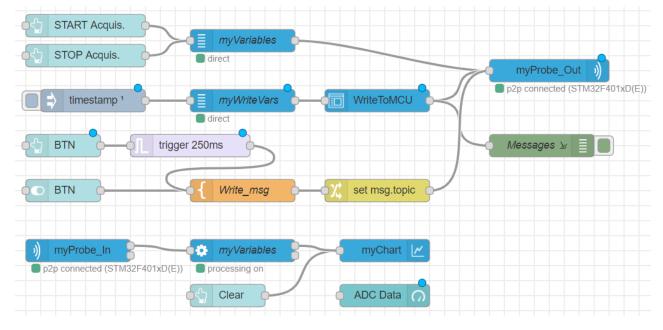

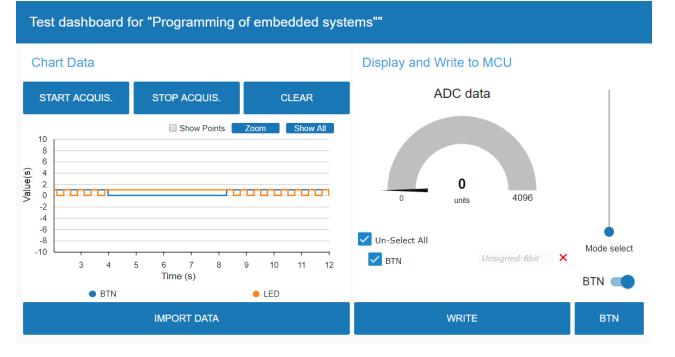

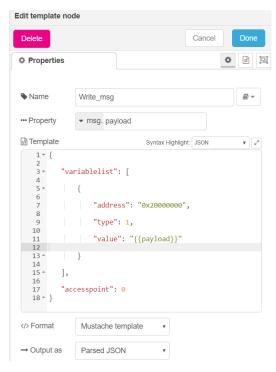

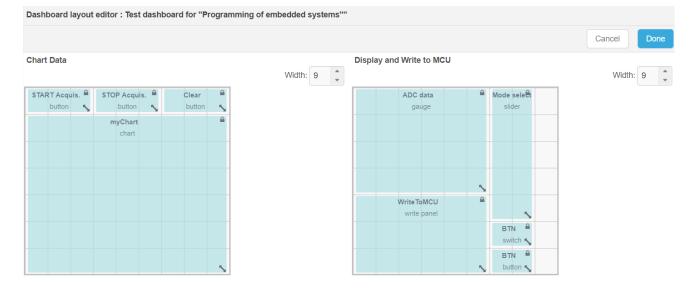

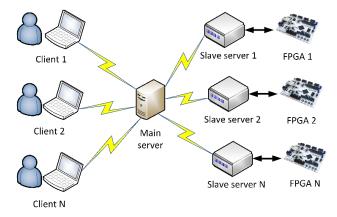

Fig. 1. Laboratory work place.

Fig. 2. Laboratory work place [5].

It is more difficult with practical tasks. They should not be long, mandatory for the student and with increasing difficulty from task to task. Laboratory work, like working in software (for a theoretical course) or with hardware (for microcontrollers and FPGAs), is more difficult in a remote implementation. And we really have little experience in conducting classes with hardware and providing students

II International Scientific and Practical Conference Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs

# MC&FPGA-2020

with access to the equipment of the department (Fig. 1 and Fig. 2).

Alternatively, in the software, the student writes a program on his remote computer. This will require the installation of specialized software on his computer. But then the student will have the opportunity to perform all operations up to loading the program into the board and incircuit debugging on a remote computer. Upon successful completion of this part, the student should be provided with remote access to the board physically located in the department. And to the measuring instruments correctly connected to the board. To implement such a regime, a sequence of problems arises.

Problem 1. It is necessary to organize the provision of remote access to the student's hardware by means of the operating system or third-party software. Distribute available computers, boards and measurement equipment to students and avoid conflicts.

Problem 2. At the first stage, it is likely that laboratory technicians are required to support such exercises. In addition to mechanical and logical connections, the staff must be able to complete laboratory work in full and be prepared for non-standard situations.

Problem 3. It is necessary to think about whether it is possible to compose and implement tasks for laboratory work with a board, automatically checked online. Or, nevertheless, without physical contact, everything will degenerate into a demonstration to the student on video how someone is doing laboratory work.

Today, there are many organizational and technical issues that have to be solved in the near future to improve the quality of distance education.

#### REFERENCES

- [1] Coursera. 100% online education Official website http://www.coursera.org/

- [2] F. Morgan et al., "Remote FPGA Lab with Interactive Control and Visualisation Interface," 2011 21st International Conference on Field Programmable Logic and Applications, Chania, 2011, pp. 496-499, doi: 10.1109/FPL.2011.98.

- [3] Nicole Hemsoth, Timothy Prickett Morgan FPGA Frontiers: New applications in reconfigurable computing. Xilinx, Published by Next Platform Press, 2017, 87 p.

- [4] Quartus® Prime Standard Edition Handbook. Intel Corp., 2017.

- [5] Valerii Semenets, Liliia Saikivska, Iryna Svyd, Oleksandr Maltsev. Trends in Training Modern Technicians. // First International Scientific and Practical Conference «Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs» MC&FPGA-2019, Kharkiv, Ukraine, July 26-27, 2019, pp. 35-36. doi: 10.35598/mcfpga.2019.013

- [6] Iryna Svyd, Oleksandr Maltsev, Oleg Zubkov, Liliia Saikivska. Matlab Use in Design of Digital Systems on the FPGA in CAD Xilinx VIVADO. // First International Scientific and Practical Conference «Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs» MC&FPGA-2019, Kharkiv, Ukraine, July 26-27, 2019, pp. 29-30. doi: 10.35598/mcfpga.2019.010

- [7] V. Semenets, I. Svyd and L. Saikivska, "Methods of improving the quality of preparation of technical specialists", inEngineering education: challendes and developments: materials of the IX International Scientific and Methodological Conference, Minsk, Belarus, 2018, pp. 415-416.

- [8] V.S. Chumak, I.V. Svyd. Testimonial Modern trends in the training of technical specialists. // Modern education - accessibility, quality, recognition: a collection of scientific papers of the XI International Scientific and Methodological Conference, November 13-14, 2019, Kramatorsk - Kramatorsk: DSEA, 2019. - pp. 245-247.

- [9] I.V. Svyd, O.V. Litvinenko, O.G. Bilotserkivets. Features of designing digital devices based on Xilinx FPGA in CAD Vivado HLx Design Suite. // Specialized Exhibition "KharkivProm Days. Production and efficiency". Collection of materials of the forum section "Automation, electronics and robotics. Development Strategies and Innovative Technologies". - Kharkiv, KNURE, Exhibition Company ADT, 2019, pp. 43-44.

- [10] V. Semenets, "Technical aspects for development laboratory base for learning FPGA and microcontroller systems.", in 10th International Conference The Experience of Designing and Application of CAD Systems in Microelectronics, Lviv-Polyana, Ukraine, 2009, p. 145.

- [11] Oleg Zubkov, Iryna Svyd, Oleksandr Maltsev, Liliia Saikivska. Incircuit Signal Analysis in the Development of Digital Devices in Vivado 2018. // First International Scientific and Practical Conference «Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs» MC&FPGA-2019, Kharkiv, Ukraine, July 26-27, 2019. – Kharkiv: 2019. – P. 12-13. DOI: 10.35598/mcfpga.2019.003

- [12] V. Semenets, V. Levikin and V. Sayenko, "Research and analysis of the didactic policy of the university in the training of specialists in information technology", Automated control systems and devices, vol. 175, pp. 4-14, 2018.

- [13] O. Avrunin, O. Kruk, T. Nosova and V. Semenets, "Technical aspects of the development of virtual laboratory works on technical educational disciplines", Open Education, vol. 3, pp. 11-17, 2008.

- [14] V. Kobzev, V. Semenets and V. Filatov, "Components of the information system for monitoring the quality of education in Kharkov National University of Radio Electronics", in 7th Int. scientific and technical conf. Information systems and technologies (IST-2018), Kharkiv-Koblevo, 2018, pp. 51-54.

- [15] O. Avrunin, S. Sakalo and V. Semenetc, "Development of up-to-date laboratory base for microprocessor systems investigation", in 19th International Crimean Conference Microwave and Telecommunication Technology CriMiCo - 2009, Sevastopol, Ukraine, 2019, pp. 301-302.

# Creation Features of Devices for Testing Nasal Breathing

Yana Nosova ORCID 0000-0003-4310-5833 Department of Biomedical Engineering Kharkiv National University of Radio Electronics Kharkiv, Ukraine yana.nosova@nure.ua

Ibrahim Younouss Abdelhamid ORCID 0000-0003-2611-2417 Department of Biomedical Engineering Kharkiv National University of Radio Electronics Kharkiv, Ukraine ibrahim.younouss.abdelhamid@nure.ua Maksym Tymkovych ORCID 0000-0001-5613-1104 Department of Biomedical Engineering Kharkiv National University of Radio Electronics Kharkiv, Ukraine oleh.avrunin@nure.ua

Oleg Avrunin ORCID 0000-0002-6312-687X Department of Biomedical Engineering Kharkiv National University of Radio Electronics Kharkiv, Ukraine maksymtymkovych@nure.ua

*Abstract*—The article is devoted to the questions of metrological certification of tests of the device of rhinomanometry type PRX. The main stages of the methodology of metrological certification, as well as design and technological aspects in the development of rhinomanometers with a measuring unit are described.

Keywords—respiratory, rhinomanometry, pressure drop, nasal breathing

# I. INTRODUCTION

In Ukraine, protecting public health is one of the most important state tasks [1, 2] aimed at organizing and increasing the production of domestic medical equipment, improving the quality of medical care, and introducing standards for the provision of medical care based on the principles of evidence-based medicine.

However, the creation of an effective system of diagnostic and therapeutic measures in Ukrainian clinics is hampered by the insufficient provision of medical facilities with modern medical equipment, since up to 70% of the medical equipment used is physically worn out, morally obsolete and needs to be replaced [2].

At the same time, the needs for medical equipment are met at the expense of domestic manufacturers by no more than 30% [2]. It follows that the use of scientific and technological potential to increase the range of domestic medical equipment products, the ability to compete in both domestic and foreign markets, is a strategic task for Ukrainian medical instrument making.

# Relevance and purpose of research.

Recently, there has been a significant increase in the prevalence of upper respiratory tract diseases [3]. However, in Ukraine, in clinical practice, instrumental methods for examining the respiratory function of the upper respiratory tract and the corresponding rhinomanometry devices are rarely used. The rhinomanometry method involves Sofia Khudaieva ORCID 0000-0002-1247-5279 Department of Biomedical Engineering Kharkiv National University of Radio Electronics Kharkiv, Ukraine sofia.khudaieva@nure.ua

Birgit Glasmacher ORCID 0000-0002-2452-1666 Institute for Multiphase Processes Leibniz University of Hannover Hannover, Germany secretariat@imp.uni-hannover.de

measuring the pressure drop across the nasal passages and the corresponding air flow during breathing to determine the value of the aerodynamic drag coefficient [4].

Currently, there are only a few rhinomanometer models on the market of medical respiratory equipment, the main of which are ATMOS 200 and ATMOS 300 (ATMOS Medical system GMB, Germany) [4, 5] and their analogues, for example, Rinolan rhinomanometer from Mitsar (RF, St. Petersburg). All of the above rhinomanometers are based on the method of anterior active rhinomanometry, which, according to the developers, is the least uncomfortable for the patient, but has limited diagnostic capabilities.

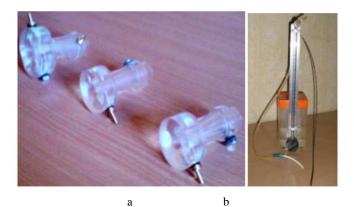

Therefore, it is relevant to create domestic rhinomanometric equipment that allows expanding diagnostic capabilities and increasing the reliability of the measured indices of nasal breathing, as well as the development of metrological certification and verification methods for both newly created and existing devices.

Formulation of the problem.

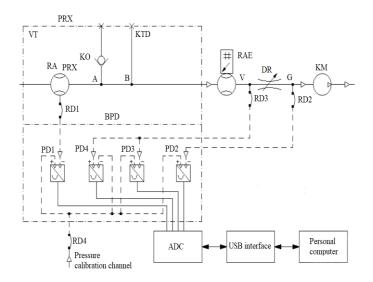

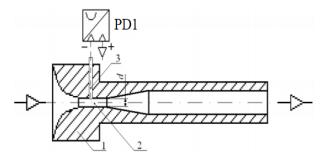

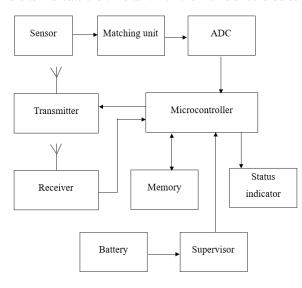

The object of the test is an experimental model of a device developed at KHNURE for determining the differential flow rate characteristics (PRX) in low pressure air ducts, which is part of the KRM computer rhinomanometry for testing nasal breathing of the TNDA of the PRX type. A detailed description of the structural diagram and design of the PRX device is given in [4, 6]. It consists of: a measuring unit containing pressure and air flow sensors, the signals from which are transmitted to the converter unit, in which the output signals of the sensors are digitized using an analog-to-digital converter and transferred via USB to a personal computer of the PC in which high-level signal processing, visualization, analysis and recording of measurement results.

The justification of the diagnostic indicators of the rhinomanometry method is given in [4], therefore, further we consider only the numerical values of the parameters of the measured quantities and the basic medical and technical requirements:

- the maximum pressure drop in the nasal passages can reach values up to 40 kPa;

- the maximum air flow during breathing in the inspiration cycle according to spirometry is up to 81/s [2];

- the measurement range of auxiliary sensors that determine the pressure drop in the submask space during inhalation and exhalation can be selected on the basis of the assumption that the aerodynamic resistance of the inlet breathing equipment (mask and connecting hoses) is not less than an order of magnitude lower than the aerodynamic resistance of the respiratory tract, which is confirmed experimentally [4, 6];

- when choosing analog sensors, it is necessary to take into account that the error of most standard primary transducers used in medical equipment for breathing diagnostics is about 5%, and the quantization step when digitizing an analog signal should be less than 10% of the measurement error. Therefore, the quantization step should not exceed 0.5% of the maximum signal value, which corresponds to 256 levels of an 8-bit ADC;

- given that the duration of the breathing cycle can be from 0.5 to 10 s [2, 4, 8], as well as the possibility of conducting examinations in dynamic mode when studying the relatively high-frequency components (up to tens of Hz) of the air flow signal in diagnosing the function of the nasal valve [8], it is necessary, accordingly with the sampling theorem, to select the sampling frequency of the measuring signals of the order of hundreds of Hz;