# III International Scientific and Practical Conference

# Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs

# MC&FPGA-2021

**Conference Proceedings**

Kharkiv, Ukraine June 24-25, 2021 III International Scientific and Practical Conference «Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs» MC&FPGA-2021, Kharkiv, Ukraine, June 24-25, 2021. – Kharkiv, NURE. – 52 pp.

There proceedings depict: mathematical modeling of information signals and systems; hardware description languages; systems of computer aided design of devices on microcontrollers, microprocessors and FPGAs; features of device development on microcontrollers and microprocessors; aspects of the development of devices in the FPGA; architecture and microprocessor technology; the problem of improving the quality of training specialists.

### Papers are presented in authors' edition.

Edition prepared of the Department of Microprocessor Technologies and Systems Faculty of Information Radio Technology and Technical Information Protection of the Kharkov National University of Radio Electronics with the support of the State Scientific Institution "Institute of Education Content Modernization" of the Ministry of Education and Science of Ukraine.

Head of the Department of Microprocessor Technologies and Systems Phone: +38 (050) 4061-220 E-mail: mcfpga@nure.ua , iryna.svyd@nure.ua Conference on Web: mcfpga.nure.ua

### Committees

| Valerii<br>Semenets        | Chair of the program committee, chair of the organizing committee, doctor of technical sciences, professor, rector of KhNURE (Kharkiv, Ukraine).                                                                                                                                                                        |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Igor Ruban                 | Vice Chair of the Program Committee, Member of the Organizing Committee,<br>Doctor of Technical Sciences, Professor, First Vice-Rector of Kharkiv National<br>University of Radio Electronics (Kharkiv, Ukraine).                                                                                                       |

| Murad Anver<br>oglu Omarov | Vice Chair of the Program Committee, Member of the Organizing Committee,<br>Doctor of Technical Sciences, Professor, Vice-Rector on International Cooperation<br>of Kharkiv National University of Radio Electronics (Kharkiv, Ukraine).                                                                                |

| Iryna Svyd                 | Vice Chair of the Program Committee, Member of the Organizing Committee,<br>Candidate of Technical Sciences, Associate Professor, Head of Department of<br>Microprocessor Technologies and Systems of Kharkiv National University of Radio<br>Electronics (Kharkiv, Ukraine).                                           |

| Paweł<br>Komada            | Member of the Program Committee, Ph.D. Eng. assistant professor, Deputy Director<br>of the Institute for General Affairs Lublin University of Technology, Institute of<br>Electronics and Information Technology, (Lublin, Poland).                                                                                     |

| Nikolai<br>Listopad        | Member of the Program Committee, doctor of technical sciences, professor, Head of<br>Department of Information Radio Technologies Belarusian State University of<br>Informatics and Radioelectronics (Minsk, Republic of Belarus).                                                                                      |

| Vahid<br>Meghdadi          | Member of the Program Committee, professor, professor the University of Limoges (Limog, France).                                                                                                                                                                                                                        |

| Serhat Şeker               | Member of the Program Committee, Prof. Dr., Dean of Faculty of Elecrical – Electronis Engineering the Istanbul Technical University (Istanbul, Turkey).                                                                                                                                                                 |

| Sergey Sakalo              | Vice Chair of the Organizing Committee, Member of the Program Committee,<br>Candidate of Technical Sciences, Associate professor, Senior Researcher, Dean of<br>Faculty of Information Radio Technologies and Technical Information Security of<br>Kharkiv National University of Radio Electronics (Kharkiv, Ukraine). |

| Aleksandr<br>Korotkevich   | Member of the Organizing Committee, Candidate of Technical Sciences, Associate<br>Professor, Dean of Faculty Radio Engineering and Electronics Belarusian State<br>University of Informatics and Radioelectronics (Minsk, Republic of Belarus).                                                                         |

| Vladimir<br>Kartashov      | Member of the Program Committee, Member of the Organizing Committee, doctor<br>of technical sciences, professor, Head of Department of the Media Engineering and<br>Information Radio Electronic Systems of Kharkiv National University of Radio<br>Electronics (Kharkiv, Ukraine).                                     |

| Ivan Antipov               | Member of the Program Committee, Member of the Organizing Committee, doctor<br>of technical sciences, professor, Head of Department of Computer Radio<br>Engineering and Technical Information Security Systems of Kharkiv National<br>University of Radio Electronics (Kharkiv, Ukraine).                              |

| Olena<br>Voloshchuk        | Member of the Organizing Committee, Ph.D, Assistant Rector of Kharkiv National University of Radio Electronics (Kharkiv, Ukraine).                                                                                                                                                                                      |

| Tetiana<br>Tkachova        | Member of the Organizing Committee, Candidate of Technical Sciences, Associate<br>Professor, Chief of Department of International Relations of Kharkiv National<br>University of Radio Electronics (Kharkiv, Ukraine).                                                                                                  |

| Volodymyr<br>Kobziev    | Member of the Program Committee, Member of the Organizing Committee,<br>Candidate of Technical Sciences, Senior Researcher, Associate Professor of the<br>Department of Applied Mathematics of Kharkiv National University of Radio<br>Electronics (Kharkiv, Ukraine).       |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oleg Sharpan            | Member of the Program Committee, Doctor of Technical Sciences, Professor,<br>Professor of the Department of Theoretical Foundations of Radio Engineering at the<br>National Technical University of Ukraine "Igor Sikorsky Kyiv Polytechnic Institute<br>(Kyiv, Ukraine).    |

| Kostiantyn<br>Dergachov | Member of the Program Committee, Candidate of Technical Sciences, Associate<br>Professor, Senior Researcher, Head of the Department of Aircraft Control Systems<br>of National Aerospace University "Kharkiv Aviation Institute" (Kharkiv, Ukraine).                         |

| Ivan Obod               | Member of the Program Committee, Member of the Organizing Committee, Doctor<br>of Technical Sciences, Professor, Professor of Department of Microprocessor<br>Technologies and Systems of Kharkiv National University of Radio Electronics<br>(Kharkiv, Ukraine).            |

| Oleksandr<br>Vorgul     | Member of the Program Committee, Member of the Organizing Committee, Ph. D. of Technical Sciences, Assosiate Professor, Assosiate Professor of Department of Microprocessor Technologies and Systems of Kharkiv National University of Radio Electronics (Kharkiv, Ukraine). |

| Oleg Zubkov             | Member of the Program Committee, Member of the Organizing Committee, Ph.D.,<br>Associate Professor, Assosiate Professor of Department of Microprocessor<br>Technologies and Systems of Kharkiv National University of Radio Electronics<br>(Kharkiv, Ukraine).               |

| Pavlo Galkin            | Member of the Program Committee, Senior Lecturer of Design and Operation of Electronic Devices Department of Kharkiv National University of Radio Electronics (Kharkiv, Ukraine).                                                                                            |

| Natalya Boiko           | Member of the Organizing Committee, Head of the Training Laboratory of Department of Microprocessor Technologies and Systems of Kharkiv National University of Radio Electronics (Kharkiv, Ukraine).                                                                         |

| Valeriia<br>Chumak      | Member of the Organizing Committee, Secretary of the conference, Laboratory<br>Assistant of Department of Microprocessor Technologies and Systems of Kharkiv<br>National University of Radio Electronics (Kharkiv, Ukraine).                                                 |

### **Table of Contents**

| No. | Paper Title                                                                                                                                                                                                 | Page<br>No. |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.  | <b>Features of the digital filters implementation on STM32 microcontrollers</b><br><i>Oleg Zubkov, Iryna Svyd, Aleksandr Vorgul</i>                                                                         | 6           |

| 2.  | Using FPGA Structures For Automotive Electronics<br>Vladimir Karnaushenko, Alexander Borodin                                                                                                                | 9           |

| 3.  | Using Benchmark Tests for Research State Memory Encoding in Finite State Machine<br>Olga Zaichenko, Nataliia Zaichenko, Pavlo Galkin, Roman Tsekhmistro                                                     | 11          |

| 4.  | <b>FPGA Implementation of Floating-Point Significand Multiplier</b><br><i>Artem Didenko, Irina Zeleneva</i>                                                                                                 | 13          |

| 5.  | Use of microprocessor-based debug modules for the development of GPS (GPRS) and GSM communication devices                                                                                                   | 15          |

| 6.  | Murad Omarov, Roman Tsekhmistro, Semen Suhorukov, Serhii Shapovalov<br>The use of intelligent microprocessor modules for working with sound communication<br>in the development of educational equipment    | 18          |

| 7.  | Volodymyr Kartashov, Roman Tsekhmistro<br>Hardware of monitoring the identity of operating cycles of diesel generator<br>Oleksandr Yenikieiev, Liudmyla Nechvoloda, Dmitriy Zaharenkov, Katerina Krykunenko | 20          |

| 8.  | <b>The development of soft skills for professional activity (Trend or reality)</b><br><i>Valentyn Korniienko, Olha Myttseva</i>                                                                             | 23          |

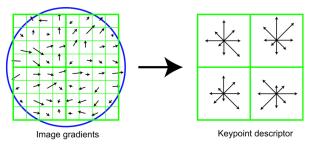

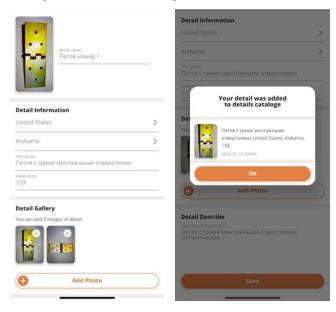

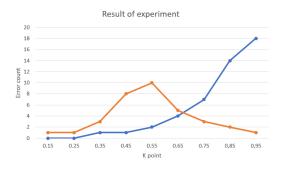

| 9.  | Automated module for product identification by their visual characteristics<br>Sergiy Novoselov, Oksana Sychova, Yevhenii Pashchenko                                                                        | 25          |

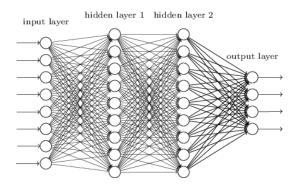

| 10. | <b>Neuron Networks Design in Matlab and Vivado</b><br>Aleksandr Vorgul, Iryna Svyd                                                                                                                          | 29          |

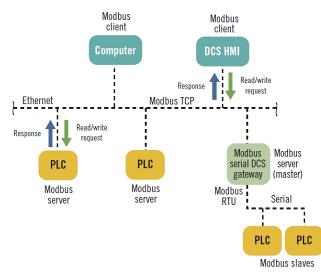

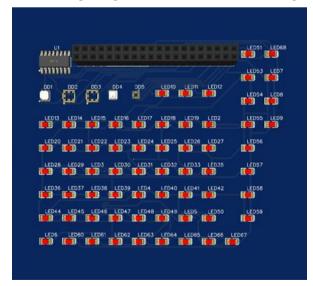

| 11. | <b>Study of the method of information transfer to LED matrix according to the ModBus</b><br><b>protocol</b><br><i>Sergiy Novoselov, Serhii Tesliuk</i>                                                      | 32          |

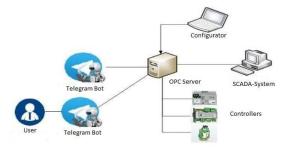

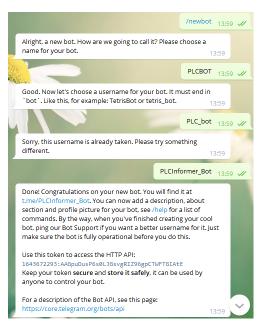

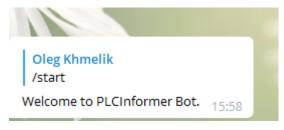

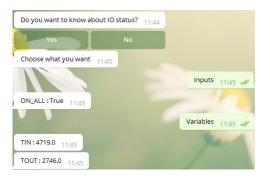

| 12. | <b>Development of a Telegram bot for receiving data from OPC servers</b><br>Oleg Khmelik, Pavlo Galkin                                                                                                      | 37          |

| 13. | <b>Development of the testbench base on STM32 microcontroller and expansion module</b><br><i>Tatiana Litvinenko, Mikhail Kuznetsov, Pavlo Galkin</i>                                                        | 39          |

| 14. | <b>Features of the design of a telemedicine complex of a wide profile based on FPGA</b><br>Valerii Semenets, Valeriia Chumak, Iryna Svyd, Oleg Zubkov, Oleksandr Vorgul,<br>Natalia Boiko                   | 41          |

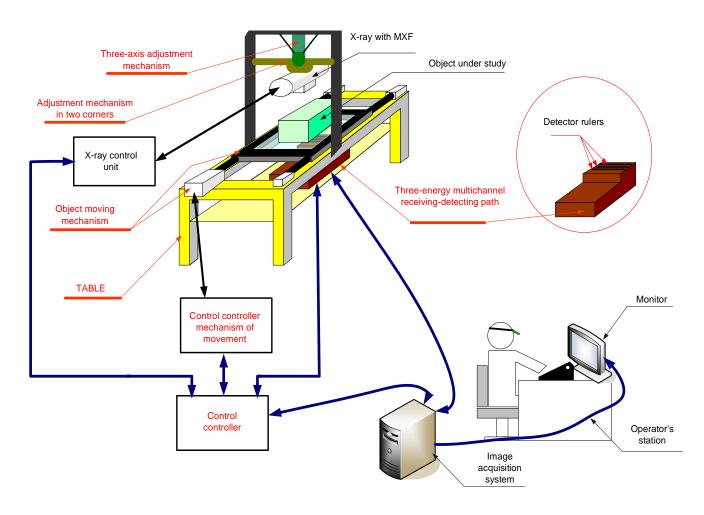

| 15. | <b>Digital System for Customs Inspection of Baggage in High Security Areas</b><br><i>Victoria Bulaga</i>                                                                                                    | 43          |

| 16. | <b>Designing the Structure of a General-Purpose Telemedicine Complex</b><br>Valerii Semenets, Valeriia Chumak, Iryna Svyd, Oleg Zubkov, Oleksandr Vorgul,<br>Natalia Boiko                                  | 47          |

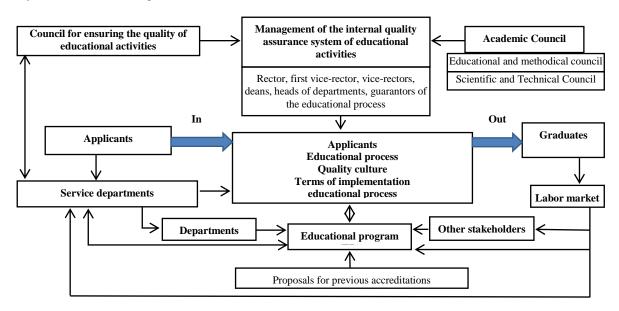

| 17. | Aspects of Quality Assurance of the Educational Process of Higher Technical<br>Education<br>Valerii Semenets, Iryna Svyd, Oleksandr Vorgul, Valeriia Chumak, Olha Myttseva,<br>Natalia Boiko                | 49          |

# Features of the Digital Filters Implementation on STM32 Microcontrollers

Oleg Zubkov ORCID 0000-0002-8528-6540 Department of Microprocessor Technologies and Systems Kharkiv National University of Radio Electronics Kharkiv, Ukraine oleh.zubkov@nure.ua Iryna Svyd ORCID 0000-0002-4635-6542 Department of Microprocessor Technologies and Systems Kharkiv National University of Radio Electronics Kharkiv, Ukraine iryna.svyd@nure.ua

Abstract—The purpose of this work is to study the efficiency of compilation of digital filters software implementation for STM32 microcontrollers. The research included: the stage of filter synthesis according to its amplitude-frequency characteristic and order, analysis of the signal at the filter output for various types of the program code optimization. As a result of the research, practical recommendations were given for choosing a compiler and the level of optimization in devices containing digital filters.

### *Keywords—compiler, microcontroller, optimization, low pass filter, frequency response*

### I. INTRODUCTION

Digital signal filtering is widely used in modern electronic technology. It is used in: positioning and navigation devices, radar signal processing, multimedia and communication technology, etc. [1, 2] Digital signal filtering allows you to isolate a useful signal from the background of noise or suppress interference spectral components. To implement a digital filter, time sampling and quantization of the analog signal amplitude is performed using an analog-todigital converter (ADC). After that, the obtained samples are processed using filters with a finite or infinite impulse response (FIR or IIR). The filtering result can be written to a information storage or fed to a digital-to-analog converter (DAC).

Digital filters today are implemented in hardware or software. For hardware implementation, FPGAs are most often used [3-5], which allows achieving high performance and processing signals at frequencies up to several GHz. However, such devices are expensive and require significant financial resources for software development. In most devices for industrial and domestic use, digital filters are implemented in software on specialized DSP processors or general-purpose controllers [6].

In recent years, STM32 controllers have been widely used in industrial, communication, multimedia devices [7, 8]. The F4, F7, H7 series of these controllers have a DSP module that allows you to perform floating point calculations at the hardware level, which reduces signal processing time. The microcontroller manufacturer provides information out filter performance for various microcontroller series. However, the effectiveness of the filter depends on the result of the program compilation. Various compilers are used in Oleksandr Vorgul ORCID 0000-0002-7659-8796 Department of Microprocessor Technologies and Systems Kharkiv National University of Radio Electronics Kharkiv, Ukraine oleksandr.vorgul@nure.ua

modern software development environments STM32CubeIDE, IAR, etc. The user is also given the opportunity to select the levels of program optimization. However, when optimizing a program, the compiler can simplify the program code, which can affect the accuracy of calculations or cancel certain actions. Therefore, the purpose of these studies was to study the effect of using different compilers and optimization modes on the performance and implementation correctness of the filter.

### II. DESIGNING A DIGITAL FILTERING DEVICE ON STM32

### A. Filter type selection and its parameters calculation

For practical implementation, a low-pass FIR filter was chosen. For high-quality suppression of interference or outof-band emissions in practical tasks, high-order filters from the 30th to the 200th are used, depending on the technical requirements for the filter. To calculate the filter coefficients, we used the Filter Builder utility from the Matlab R2014b package [9-11]. 2 filters of the 50th and 100th orders were designed. The mathematical description of the 100th order filter has the form

$$y(n) = \sum_{i=n}^{n-100} x(i) \cdot b(i-n), \qquad (1)$$

where y(n) is the signal value at the filter output, x(i) are the input signal samples, which are stored in the filter memory cells, b(i-n) are the filter coefficients.

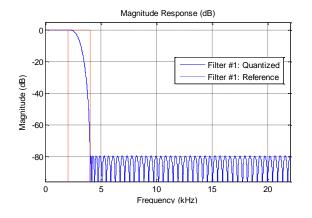

Fig. 1 shows the amplitude-frequency characteristic (AFC) of the synthesized filter of the 100th order.

The sampling frequency of the signal at the filter input is 44 kHz. The cutoff frequency of both filters is 2 kHz, the frequency of filter suppression is 4 kHz. Suppression of spectral components at frequencies above 4 kHz in the 50th order filter is 43dB, and in the 100th order filter at least 79dB. The calculated filter coefficients are 32 bit real numbers.

Fig. 1. Frequency response of the synthesized low-pass filter.

### B. Hardware implementation of the filter

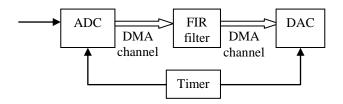

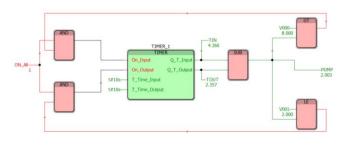

The STM32F407VG microcontroller with a core clock frequency of 168 MHz was chosen as the hardware platform. This microcontroller contains a built-in 12-bit ADC and DAC. Also, due to the presence of a built-in multi-channel controller for direct memory access (DMA), it is possible to transfer the results of analog-to-digital conversion to RAM and samples from the filter output to the DAC in parallel with the execution of the main task. The timing of the start of converting the analog signal to digital form and digital samples to analog voltage is set by the timer. It generates internal events, according to which the ADC and DAC work synchronously. Then the functional diagram of the digital filtering device on the STM32F407VG has the form (Fig.2).

Fig. 2. Functional diagram of the filtration device.

During the research, the developed digital filter worked in two modes: without input data buffering and with input data buffering. In the first mode, when one sample of the analog signal arrived from the ADC, it was fed to the input of the filter and the result of filtering through the DMA channel was fed to the input of the DAC. In the second mode, 128 samples of the input signal were transferred to the RAM buffer via the DMA channel. Upon completion of the buffer filling, an interrupt from the DMA channel was generated and the contents of the buffer were filtered. The filtered data array was transferred to the DAC. The second mode is more efficient, since it takes a certain amount of time to enter and exit the interrupt when processing single samples.

During the research, generator Siglent sdg 2122 was used to generate signals at the ADC input. The signal at the DAC output was investigated using an Intrustar ISDS 220B USB oscilloscope and an Siglent SSA3021 spectrum analyzer.

### III. RESEARCH RESULTS

To study the software implementation of the filter, the two most popular development platforms IAR Embedded Workbench 8.3 and STM32CubeIDE 1.4 were selected. The first platform has a certified compiler and the ability to choose one of 4 optimization modes: None - no optimization, Low, Medium, High. Produce microcontrollers offers its own development environment STM32CubeIDE, which uses the free popular GCC compiler. In this platform, the user can also select the optimization level: O0 - no optimization, O1 - the main optimization level tested on many tasks, Og - the lowest optimization level for debug mode, O2 - speed optimization with increasing code, O3 - speed optimization with increasing code, O3 - speed without increasing the code, Ofast - maximum performance.

The main parameters for the study were: the speed of the filter (loading the microcontroller to perform filtering operations), the correspondence of the filter characteristics to those obtained during synthesis

Table 1 shows the results of studying the filter speed and the results of measuring the attenuation in the suppression band after compiling the program in the IAR Embedded Workbench.

TABLE I. RESEARCH RESULTS FOR IAR EMBEDDED WORKBENCH

| Parameter      |       |       | Op    | timization |        |        |  |

|----------------|-------|-------|-------|------------|--------|--------|--|

|                | No    | one   | 1     | Low        | Medium |        |  |

|                |       |       | Fil   | ter order  |        |        |  |

|                | 50    | 100   | 50    | 100        | 50     | 100    |  |

| Efficiency     | 12,3/ | 24,1/ | 11,9/ | 23,97/     | 6,45/  | 13,05/ |  |

| without/with   | 11,9  | 23,5  | 11,6  | 22,9       | 6,13   | 12,09  |  |

| buffer, μs     |       |       |       |            |        |        |  |

| Attenuation on | 39    | -70   | 39    | -65        | -9     | -20    |  |

| 4kHz, dB       |       |       |       |            |        |        |  |

When using the optimization levels Medium and High, the suppression of spectral components above 4 kHz does not match the synthesis results. Therefore, when using the IAR Embedded Workbench to compile digital filter code, optimization levels higher than Low should not be used.

Table 2 shows the results of studying the speed of the filter and the results of measuring the attenuation in the suppression band after compiling the program in the STM32CubeIDE environment.

TABLE II. RESEARCH RESULTS FOR STM32CUBEIDE

| Parameter      |              |       | Ор   | timization |      |      |  |  |  |  |  |  |  |

|----------------|--------------|-------|------|------------|------|------|--|--|--|--|--|--|--|

|                | 6            | 00    |      | Og         | (    | 01   |  |  |  |  |  |  |  |

|                | Filter order |       |      |            |      |      |  |  |  |  |  |  |  |

|                | 50           | 100   | 50   | 100        | 50   | 100  |  |  |  |  |  |  |  |

| Efficiency     | 20/          | 37,9/ | 7,9/ | 15,5/      | 4,2/ | 8,3/ |  |  |  |  |  |  |  |

| without/with   | 17,6         | 28,9  | 6,3  | 12,8       | 3,8  | 6,5  |  |  |  |  |  |  |  |

| buffer, µs     |              |       |      |            |      |      |  |  |  |  |  |  |  |

| Attenuation on | 39           | -70   | 39   | -40        | -12  | -23  |  |  |  |  |  |  |  |

| 4kHz, dB       |              |       |      |            |      |      |  |  |  |  |  |  |  |

When using STM32CubeIDE to compile a software implementation of a digital filter, it is unacceptable to use optimization levels higher than Og, since the measured filter characteristics do not correspond to the synthesis results. The usage of data buffering can reduce processing time by up to 18%.

### **IV.** CONCLUSIONS

In the absence of optimization, the program compiled in the STM32CubeIDE environment is inferior in performance to the program compiled in the IAR Embedded Workbench environment. However, at the first level of optimization, the controller manufacturer's GCC compiler provided a significant performance advantage over the IAR Embedded Workbench compiler. Application of any optimization types in STM32CubeIDE leads to a significant deviation of the filter characteristics from the calculated ones.

#### REFERENCES

- Tirthadip Sinha,JaydebBhaumik, "Design of Computationally Efficient Sharp FIR Filter Utilizing Modified Multistage FRM Technique for Wireless Communications Systems" *Journal of Electronic Science and Technology*, Volume 17, Issue 2, 2019, pp. 185-192.

- [2] Yuan Xu, Yuriy S Shmaliy, Luchi Hua, Liyao Ma and Yuan Zhuang, "Decision tree-extended finite impulse response filtering for pedestrian tracking over tightly integrated inertial navigation system/ultra wide band data", *Measurement Science and Technology*, Volume 32, Number 3, 2021, pp.217-228.

- [3] Sumbal Zahoor, Shahzad Naseem, "Design and implementation of an efficient FIR digital filter" *Cogent Engineering* vol. 4, 2017, pp. 123-135.

- [4] Pandey, B., Jain, A., Kumar, P., Hussain, A., Levy, J. y Chowdhry, B. S. "Energy Efficient and High–Performance FIR Filter Design on Spartan–6 FPGA". *3C Tecnología. Glosas de innovación aplicadas a la pyme*. Edición Especial, Mayo 2019, pp. 36–49.

- [5] I. Svyd, O. Maltsev, L. Saikivska and O. Zubkov, "Review of Seventh Series FPGA Xilinx", *I International Scientific and Practical Conference*, 2019. doi: 10.35598/mcfpga.2019.008.

- [6] Moutaman Mirghani, "Implementation of Matched Filters Using Microcontrollers", *Conference of Basic Sciences and Engineering Studies* (SGCAC), 2016, pp. 62-66.

- [7] O. Zubkov, "Teaching trends in the design of electronic devices on microcontrollers". Specialized show "KharkivProm Days. Wi-Fi and Efficiency ". Collection of materials in the forum of the section "Automation, electronics and robotics. Development strategy and innovation technologies". - Kharkiv, KNURE, Vistavkova company ADT, 2019 .-- pp. 40-42.

- [8] O. Vorgul, O. Zubkov, I. Svyd and V. Semenets, "Teaching microcontrollers and FPGAs in Quarantine from Coronavirus: Challenges and Prospects", *MC&FPGA-2020*, 2020. doi: 10.35598/mcfpga.2020.005.

- [9] Zena Ez Dallalbashi, "MatLab Based Design and Implementation of Digita Filter" *International Journal of Computer Science and Network Security*, VOL.20 No.1, 2020, pp. 91–101.

- [10] I. Svyd, O. Maltsev, O. Zubkov and L. Saikivska, "Matlab Use in Design of Digital Systems on the FPGA in CAD Xilinx VIVADO", *I* International Scientific and Practical Conference, 2019. doi: 10.35598/mcfpga.2019.010.

- [11] Jie Zhao, "Modeling and Simulation of Digital Filter" 4th National Conference on Electrical, Electronics and Computer Engineering, 2015, pp.1333-1338.

Vladimir Karnaushenko ORCID 0000-0001-7744-2569 Department of Microelectronics, electronic devices and appliances Kharkiv National University of Radioelectronics Kharkiv, Ukraine vladimir.karnaushenko@nure.ua

*Abstract*—As microelectronics becomes increasingly important in automotive systems, transport electronics developers are increasingly relying on FPGA programmable structures to create applications with better performance and flexible architectures.

Keywords—electronic control units, transport applications, programmable logic blocks, automotive information technology, hardware, digital signal processing

### I. IMPROVING COMPUTING PERFORMANCE FOR TRANSPORT

Although cars have a long and rich history, electronics have been used extensively in transport applications relatively recently, becoming an integral part of the automotive world only in recent decades. Today, car companies compete fiercely not only with each other, but also with the latest and most modern technologies [1].

Currently, manufactured cars rely on many sensors to measure many internal and external variables that could affect the car's driving behavior, as well as additional parameters such as visibility and passenger comfort. Depending on their level of sophistication, sensors can be classified from simple sensors that directly measure individual physical parameters (eg ambient light sensors and temperature sensors) to complex intelligent sensors that determine environmental parameters using broad-spectrum signals (eg radio frequency, radars and light, video); in addition to measurements, they perform data processing and have the ability to perform drives [2].

Using processor-based electronic control units (ECUs), it is difficult to keep up with consumer electronics due to the long cycles of chip development and strict standards of reliability and quality applied to the automotive industry. The automotive industry uses increasingly sophisticated electronic systems to offer the driver better safety and efficiency. Programmable arrays of valves (FPGAs) can play an important role in filling this gap, providing up-todate performance and high flexibility to system architects to customize projects through a flexible (programmable) electronic circuit structure.

The main goal in automotive design is to reduce the total number of ECUs, as they increase the overall cost of the vehicle and reduce reliability. Thanks to the latest advances Alexander Borodin ORCID 0000-0001-7744-2569 Department of Microelectronics, electronic devices and appliances Kharkiv National University of Radioelectronics Kharkiv, Ukraine alexander.borodin@nure.ua

in FPGA structures, it is now possible to combine electronic components inside the car more intelligently.

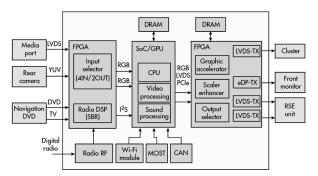

For example, the implementation of a purely hardware processor architecture is a problem that needs to be addressed urgently. However, one possible solution to these interferences is a hybrid approach that combines processors and ECUs with FPGA-based chip systems (SoC), Fig.

FPGAs contain an array of programmable logic blocks, such as built-in memory, digital signal processing units (DSPs), and high-speed receivers. With FPGAs, the automotive system becomes easily scalable with minimal hardware changes.

In this way, FPGAs create opportunities for automotive original manufacturers and suppliers to more effectively build innovative safety programs, such as adaptive cruise control, driver assistance, collision avoidance and blind spot warning.

Fig. 1. Hardware processor architecture

As the name implies, driver assistance includes fea-tures such as reversing cameras, three-dimensional sur-veillance cameras, lane departure warning systems, pe-destrian detection and more [3].

### II. HARDWARE AND SOFTWARE

FPGA is a semiconductor device based on a matrix of programmable logic blocks, which are determined by their functionality. This feature distinguishes FPGAs from specialized integrated circuits (ASICs) designed for applications designed for specific design tasks. ASICs and FPGAs have a number of key benefits that need to be carefully evaluated before making a decision. With the

III International Scientific and Practical Conference Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs

development of unmatched logic density and many other features such as digital signal processing, clock speed and high-speed serial bus, FPGAs become a reliable helper for almost any type of design.

For example, automotive infotainment systems are of great importance in modern vehicle design and have a significant impact on the sale of global vehicles. In these systems, it is important to choose the right main system processor to differentiate the user interface with the latest graphics. With several models to support, you may have to choose different SoCs due to system variations and the emergence of new interoperability technologies.

Thanks to FPGA, the system becomes easily scalable, which allows you to update the firmware remotely to support more manufacturers, regions and models with minimal hardware modifications. You can use the FPGA to support any combination of I / O interfaces [4].

The most important design factor of FPGAs is that they are programmable logic devices. Of course, CPU software can be upgraded, but the same cannot be said for computer architecture. On the other hand, FPGAs can be configured or reprogrammed to perform various functions an infinite number of times. In many recent cars, the software tracks many functions during operation. For example, Tesla models already support software updates remotely.

Thanks to this feature, FPGAs are able to constantly support the original software of manufacturers with the latest versions of programmable or customized hardware architecture systems. Such software updates can be applied to various car features, which may include more FPGAoriented structures as they become more powerful, smaller and cheaper [5].

Connected vehicles are able to analyze information in real time to provide new information to car users, optimizing their experience. Meanwhile, IoT connectivity can help develop new development models for the automotive market by transforming the relationship between automakers and drivers.

### **III. AUTOMOTIVE INFORMATION TECHNOLOGY**

As more IoT technologies are implemented in automotive applications, this is a prerequisite for the convergence of innovations - especially in the electronics in-dustry. However, experienced engineers know that there is a learning curve when using something new that comes into direct conflict with less development time. In turn, this increases the project risk.

For this reason, designers tend to reuse technologies that are already well known or have been used before. Over time, this philosophy transforms some architecture into widely used industry standards, while most others are used only in narrow market niches.

IoT engineers will have to deal with significant issues such as energy efficiency and management of incompati-ble interfaces. The FPGA-based design approach can help solve these problems by offering a fully functional hardware platform for very low-power IoT applications. When researching which 32-bit processor will best serve customers, many companies realize that the stand-ard industry architecture offers significant benefits to the owner. Standard industry processors, as a rule, have a wide range of development tools, a large number of available software codes and designers who have the knowledge and experience to use them. Such benefits ac-celerate project development time (and therefore time to market) and also reduce a project risk, which in turn pro-vides users with higher value-added solutions [6].

On this front, the ARM Cortex – M1 processor, designed from scratch for use in FPGAs, stands out. One of the main functions - it helps to minimize the amount of resources needed to meet the requirements of the devel-oper. For example, debugging functions can be enabled or removed. Operating system extensions for system tim-ers and software interrupts are not required. Cortex-M1 works with most basic FPGAs, which means that switch-ing from one FPGA device to another requires minimal effort.

### IV. CONCLUSIONS

FPGAs are now implemented separately or together with processors in many automotive systems, as they provide more efficient and faster solutions for hundreds of ECUs in a vehicle. They provide higher performance without consuming more energy, and improve customiza-tion and scaling capabilities [7].

FPGAs can also help reduce overall car ownership costs by integrating and / or reducing the number of ex-ternal components, speeding up time to market, and con-solidating accelerated project development.

In addition, thanks to innovative and cost-effective imaging solutions, FPGAs support the implementation of even more automotive features. Finally, they often offer a more cost-effective option in programs such as traffic control systems or engines. At present, it is expected that the design needs of the growing hybrid and electric vehi-cle industry will also focus on expanding the FPGA mar-ket.

#### REFERENCES

- FPGA Considerations for Automotive Applications. Rick Nicholson, Michael Gabrick, Frank Winters. Conference: SAE World Congress & Exhibition. DOI 10.4271/2006-01-0368

- [2] M. Maurer, "Forward Collision Warning and Avoidance." In: A. Eskandarian (Ed.), Handbook of Intelligent Vehicles, Springer London, 2012.

- [3] Three decades of driver assistance systems: Review and future perspective. K Bengler, K Dietmayer, B Farber, M Maurer, C Stiller, H Winner – IEEE Intelligent Transportation Systems Magazine vol. 6, no. 4, Winter 2014, pp. 6-22.

- [4] Deep multi-modal object detection and semantic segmentation for autonomous driving: Datasets, methods, and challenges, – D Feng, C Haase-Schuetz, L Rosenbaum, H Hertlein – IEEE Transactions on Intelligent Transportation Systems, 2020.

- [5] A parallel implementation of sequential minimal optimization on FPGA. DH Noronha, MF Torquato, MAC Fernandes, – Microprocessors and Microsystems 69, 138-151.

- [6] Markvollrath; Schleicher, S.; Gelau, C. The influence of Cruise Control and Adaptive Cruise Control on driving behaviour—A driving simulator study. Accid. Anal. Prev. 2011, 43, 1134–1139.

- [7] Field Programmable Counter Arrays Integration with Field Programmable Gates Arrays. Vladimir Karnaushenko, Alexander Borodin. – Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs, MC&FPGA. – 2019. – P. 14-16.

# Using Benchmark Tests for Research State Memory Encoding in Finite State Machine

Olga Zaichenko ORCID 0000-0003-4936-2785 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine olha.zaichenko@nure.ua

Pavlo Galkin ORCID 0000-002-0558-6448 dept. Design and Operation of Electronic Devices Kharkiv National University of Radioelectronics Kharkov, Ukraine pavlo.halkin@nure.ua

Abstract—The synthesizer will automatically assign the state memory codes based on the most effective use of the target technology (e.g., binary, gray code, one-hot) in FPGA. But exists alternative, when user by himself choose type of memory encoding. There was considered user defined state coding method for Quartus Altera.

Keywords—FPGA, finite state machine, state memory, memory coding, synthesizer, one-hot, sequential, johnson, optimization, speed of performance

### I. INTRODUCTION

Finite state machines can be easily modeled using the behavioral constructs in FPGA. Within the VHDL state machine model, three processes are used to describe each of the functional blocks: state memory, next state logic, and output logic[1].

The model of the state memory of the FSM using a process describes the behavior of the D-Flip-Flops in the FSM that are holding the current state on their Q outputs. Each time there is a rising edge of the clock, the current state is updated with the next state value present on the D inputs of the D-Flip-Flops. This process must also model the reset condition. At all other times, the process will simply update current\_state with next\_state on every rising edge of the clock. The process model is very similar to the model of a D-Flip-Flop. This is as expected since this process will synthesize into one or more D-Flip-Flops to hold the current state. The sensitivity list contains only clock and reset, and assignments are only made to the signal current\_state. The following syntax shows how to model the state memory of this FSM example.

The synthesizer will automatically assign the state codes based on the most effective use of the target technology (e.g., binary, gray code, one-hot). But exists alternative, when user by himself choose type of memory encoding.

The aim of the work is a comparative study of the possibilities of using the state coding methods to reduce

Nataliia Zaichenko ORCID 0000-0001-9798-7136 dept. Microelectronics, Electronic Devices and Apliances Kharkiv National University of Radioelectronics Kharkov, Ukraine nataliia.zaichenko@nure.ua

Roman Tsekhmistro ORCID 0000-0003-3628-3658 dept. Media Endineering and Information Radioelectronic System Kharkiv National University of Radioelectronics Kharkov, Ukraine roman.tsektmistro@nure.ua

increase the speed of the logic circuit of the finite state automaton.

### II. TYPES OF MEMORY ENCODING

There are variants of memory encoding. 1. "One-hot." A separate trigger is used to encode each state. The number of triggers is equal to the number of states of the machine. At any given time, only one trigger can have a single value. To form the value of each trigger, a logical equation is used, in which the number of terms is equal to the number of transitions to the corresponding state. 2. "Sequential". The synthesizer finds long sequences of states in the machine, consisting of unconditional transitions, and encodes the states within them with consecutive binary codes of minimum sufficient bit size. As a result, the address inputs of the Look-Up Table (LUT) elements are not fed to the input signals of the machine, and only the current state code is fed, which usually has a small bit compared to the number of input signals. Sequential state coding provides more optimal filling of static memory cells of LUT elements and reduces the number of unused cells. 3. Johnson. State coding is performed using Johnson code. Each value of this code contains only one continuous sequence of single bits, and any two adjacent values in an ordered sequence of values differ by only one bit. Johnson's code is a cyclic code with an excess and reduces the number of electrical interference caused by the simultaneous switching of several bits of the register circuit. Thus, when using the Johnson code to encode the states of the machine, the number of triggers involved will be greater than in the case of sequential encoding. 4. "Gray." State coding is performed using Gray code, in which two adjacent values in an ordered sequence of values differ in the value of one binary digit, and the number of bits coincides with the number in the case of sequential coding. Like Johnson's code, Gray's code should be used to encode state chains, because each automatic transition in such a chain will be accompanied by a change of only one bit in the machine's memory register. 5. "Auto". The synthesizer chooses one of the above coding methods at its discretion based on the analysis of the VHDL description of the

machine. The choice of coding method also depends on other settings (for example, on the leading optimization strategy hardware costs or speed), but the generalized approach is as follows: if the machine contains a small number of states, one-hot coding is used; with an average number of states, the Johnson code is used; with a large number of states, the Gray code is used.

### III. USING BENCHMARK TESTS FOR COMPARE SPEED OF PERFORMANCE FOR DIFFERENT STATE MEMORY ENCODING

It is known the input project is synthesized into a circuit that consists of logical elements of logical blocks in a FPGA. Quartus converts a system description in one of the hardware description languages (HDL from Hardware Description Language) into a set of microcircuit-independent functional and storage elements. After the synthesis is completed, information can be obtained on the number of LUT-elements and triggers required for its implementation, as well as the estimated maximum frequency of operation [2].

The difficulty lies in the fact that the same project can be placed in the FPGA in different ways, and there are millions of these ways. Some placement and routing is better, others are worse. The main criterion for the quality of the resulting system is the maximum frequency at which the project can operate with a given arrangement of elements and with a given routing of links. It is influenced by the length of the links between the blocks and the number of programmable switches between them. To use advanced settings that impact the synthesis of design it is necessary to access to settings. To click Assignments > Settings > Compiler Settings > Advanced Settings (Synthesis). The Optimization mode setting enables various combinations of these settings to achieve design goals.

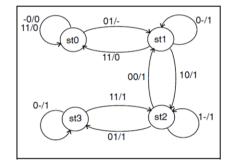

.i 2 .o 1 .p 11 .s 4 -0 st0 st0 0 11 st0 st0 0 01 st0 st1 -0- st1 st1 1 11 st1 st0 0 10 st1 st2 1 1- st2 st2 1 00 st2 st1 1 01 st2 st3 1 11 st3 st2 1

### Fig. 1. Benchmarklion in KISS2 format [5]

As it turned out, not every program is suitable for the analysis of efficiency, for example, the vending machine [1] showed the same performance for all types of encoding. So we had to turn to special state machines, benchmarks. Benchmarks have their own names [2], for example, "lion". Their number will reach more than 50 pieces. Initially, they are recorded in the KISS2 format (fig.1) The KISS2 format is a very popular text format for describing the nehavior of a control units. A KISS2 file is devided into two parts: header and a state transition table. The header contains generic parameters of control unit, i.e. the number of inputs, the number of terms.

.i <number of inputs> .o <number of outputs> .p <number of products> .s <number of states used> .r <reset state> <input> <current-state > <next-state> <output>

<input> <current-state > <next-state> <output>

### Fig. 2. Example of headers KISS2[4]

Due to application of TimeQuest Timing Analyzer from Tools Menu Quartus Altera[7] there was estimated time of performance for hybrid of finite state machine from[1] and [5,6]. The results from Report Fmax Summary are for Auto and One-Hot Encoding - 854.7MHz, for Sequential and Minimal Bits 1000 MHz, Johnson and Gray encoding 1001 MHz, which partially coincide with results from [2].

Fig. 3. Graph of the lion benchmark [6]

### IV. CONCLUSION

One can use his own User-Encoded style, or select One-Hot, Minimal Bits, Gray, Johnson, Sequential, or Auto (Compiler-selected) encoding [3]. The best speed of performance has one-hot encoding.

#### REFERENCES

- [1] B. J. LaMeres, "Introduction to Logic Circuits and Logic Design with VHDL," Springer, 2019, 503 p.

- [2] A. A. Barkalov, I. Ya. Zeleneva, E. R. Tatolov. "Analysis of the efficiency of state coding methods in the synthesis of Mealy automata on FPGA," Science of the Donetsk National Technical University, series of Problems of modeling and design automation, 2011, Vipusk 10 (197) pp. 1-6.(in Russian)

- [3] Advanced Synthesis Settings Dialog Box. [Online]. Available: https://www.intel.com/content/www/us/en/programmable/quartushelp /17.0/mapIdTopics/mwh1465495270874.htm [Accessed: 10- Jun-2021]

- [4] A. Barkalov, L. Titarenko, M. Kolopienczyk, K. Mielcarek, G.Bazydlo, Logic synthesis for FPGA-based finite state machines. Springer, 2016.

- [5] LGSynth93, International Workshop on logic synthesis benchmark suite (LGSynth93).TAR, Benchmarks test. [Online]. Available:http://www.cbl.ncsu.edu:16080/benchmarks/LGSynth93/L GSynth93.tar [Accessed: 10- Jun- 2021]

- [6] H. Kubátová, "Finite state machine implementation in FPGAs". In Design of Embedded Control Systems Springer, Boston, MA., 2005, pp. 175-184

- [7] Getting started with the TimeQuest Niming Analyzer [Online]. Available: https://www.youtube.com/watch?v=bFmTHLZ3DGs [Accessed: 10- Jun- 2021]

III International Scientific and Practical Conference Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs

# FPGA Implementation of Floating-Point Significand Multiplier

Artem Didenko ORCID 0000-0001-7556-2276 Bachelor student of Computer Engineering National University Zaporizhzhia Polytechnic Zaporizhzhia, Ukraine didenko.art121@gmail.com

*Abstract*—Development of high-performance computational devices needs fast methods of operations with numbers which are presented in floating-point format. One of the most common approaches to build a significand multiplier is using a Wallace CSA-adder tree structure which shows good performance in adding partial sums. Significand multiplier was implemented in FPGA as a part of floating-point multiplier which works with single precision numbers in IEEE-754 standard.

Keywords—multiplier, floating-point number, carry-save adder, FPGA

### I. INTRODUCTION

FPGA finds its usage in many different fields such as sorting and data search, audio, video and image processing, cryptography, processing of data packets in networks, random numbers generation. Among new important markets one can distinguish finance, bioinformatics and hardware for radio communication [1]. High performance of FPGA comes from its flexibility, which gives a possibility to realize optimized devices for specific purposes [2]. It is worth mentioning that inner structure of FPGA aslo allows to parallelize data processing.

Lots of computational devices use floating point arithmetic in their operations with numbers. Floating point numbers have such advantage as wide range, which makes them suitable in digital signal processing and scientific modeling.

Multiplication is one of most common operations which computational devices perform. There are a lot of methods of implementing floating point multiplication in hardware. Significand or mantissa multiplication is the main part of floating point multiplication algorithm, therefore much attention should be paid to a structure of significand multiplier.

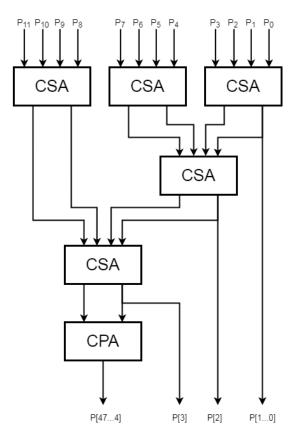

This paper describes FPGA implementation of significand multiplier which is based on CSA-adder tree. CSA-adder tree performs summation of partial sums that are generated during significands multiplication process.

### II. THEORETICAL BACKGROUND

### A. IEEE-754 Standard

In modern computers and other computational devices floating point numbers are represented according to IEEE-

Irina Zeleneva ORCID 0000-0002-4042-4540 Department of Computer Systems and Networks National University Zaporizhzhia Polytechnic Zaporizhzhia, Ukraine irina.zeleneva@gmail.com

754 standard. This standard defines single and double precision floating point numbers. Single precesion numbers are represented as one which consists of one sign bit, 8 exponent bits and 23 significand bits.

### B. Wallace multiplier

Multiplication of significands of floating-point numbers uses the same methods as fixed-point numbers multiplication. According to [3] Wallace multiplier have better performance than array multiplier which is another common method of multiplication. Wallace multiplier consists of CSA-adder tree.

Wallace multiplier is a method of acceleration of multiplication which allows to add several partial sums simultaneously. Wallace CSA-adder tree reduces several k-bit operands to two k+2 bit operands. Unlike Dadda CSA-adder tree Wallace CSA-adder tree reduces the number of operands as early as possible what minimizes the overall delay by making the final carry-propagation adder as short as possible [4].

Another method that can speed up multiplication process is high-radix multiplication which decreases number of partial sums. In this work these two methods were combined together.

### C. CSA-adder

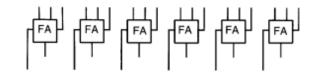

One way to add more than two operands simultaneously is to use CSA-adder. CSA-adder is a full adder without carry propagation chain. On the output of CSA-adder there are sum and carry vectors, which then can be added using usual carry-propagation adder. A typical structure of CSA-adder is shown below.

Fig. 1. Structure of CSA-adder [4]

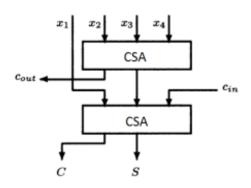

As it can be seen from fig. 1 CSA-adder adds three operands simultaneously. Another structure that adds several operands simultaneously is 4:2 compressor, which is in fact two CSA-adders. The structure of 4:2 compressor is shown below.

Fig. 2. Structure of 4:2 compressor [5]

The use of 4:2 compressors allows to simplify the structure of a multiplier.

### **III. FGPA IMPLEMENTATION**

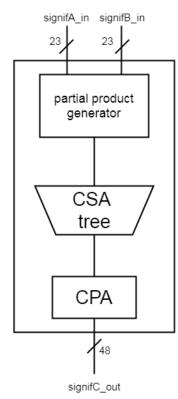

As mentioned previously significand of floating point number in IEEE-754 standard consists of 23 bits with one implicit bit will lead to 24 bits. Therefore there will be 24 partial sums. In this work Wallace radix-4 multiplier is used what decreases number of partial sums to 12. The developed structures of significand multiplier and CSA-adder tree are shown below.

Fig. 3. Structure of significand multiplier

As it can be seen from fig. 3 significand multiplier consists of partial product generator module, CSA-adder tree which reduces number of partial sums to two operands and carry-propagation adder which adds these two operands.

Fig. 4. Structure of Wallace CSA-adder tree

Significand multiplier was simulated in Modelsim and implemented on FPGA Altera Cyclone IV using VHDL. According to compilation report significand multiplier utilizes 1,196 logic elements.

#### **IV. CONCLUSION**

Significand multiplier which is based on CSA-adder tree is one of the most common ways to implement highperformance floating point multipliers. The use of significand multiplier which is based on Wallace tree in FPGA projects allows to speed-up multiplication and save embedded FPGA multiplier elements.

#### REFERENCES

- Leong, P. Recent Trends in FPGA Architectures and Applications / P.H.W. Leong // 4th IEEE International Symposium on Electronic Design, Test and Applications (delta 2008), Hong Kong, 23-25 January 2008: proceedings. – Los Alamitos: IEEE, 2008. – pp.137– 141.

- [2] Asano, S. Performance comparison of FPGA, GPU and CPU in image processing / S. Asano, T. Maruyama, Y. Yamaguchi // 2009 International Conference on Field Programmable Logic and Applications, Prague, 31 August - 2 September 2009 : proceedings. – Los Alamitos: IEEE, 2009. – P.126–131.

- [3] Bečvář M. Fixed-Point Arithmetic in FPGA / M. Bečvář, P. Štukjunger // Acta Polytechnica Vol. 45 No. 2/2005. – pp. 67–72.

- [4] Parhami, B. Computer Arithmetic: Algorithms and Hardware Designs, 2nd edition / B. Parhami. – New York : Oxford University Press, 2010. – 672 p.

- [5] Koren, I. Computer Arithmetic Algorithms 2nd Edition / I. Koren. Natick : A K Peters/CRC Press, 2001. – 296p.

# Use of Microprocessor-Based Debug Modules for the Development of GPS (GPRS) and GSM Communication Devices

Murad Omarov ORCID 0000-0003-4842-4972 Department of Natural Sciences Kharkiv National Universityof Radio Electronics Kharkiv, Ukraine murad.omarov@nure.ua

Semen Suhorukov Department of MIRES Kharkiv National Universityof Radio Electronics Kharkiv, Ukraine semen.sukhorukov@nure.ua

*Abstract*—This report is devoted to an overview of the technical characteristics and the specifics of the use of modern debugging microprocessor modules for the development of devices for geolocation of objects and data transmission over a mobile communication channel.

Keywords—microcontroller system, RASPBERRY PI, arduino ide, GSM(GPS-GPRS)-module

### I. INTRODUCTION

The success of modern technologies has made it possible to create microprocessor modules for obtaining geolocation data on the location of an object and means of transmitting the received data.

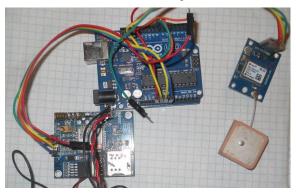

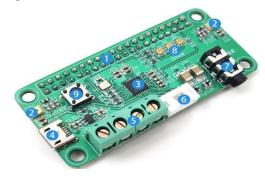

Fig. 1. GSM communication module SIM900 with USB-TTL converter for connection to a computer

One of these modules is shown in fig.1. It is a mobile communication processor, a SIM card socket, a power stabilizer, an interface for communication with a PC and an external microprocessor [2].

SIM800C is the world's smallest GSM / GPRS module in an LCC case with end contacts. Its distinctive features, in addition to its ultra-miniature size, are support for Bluetooth Roman Tsekhmistro ORCID 0000-0003-3628-3658 Department of MIRES Kharkiv National Universityof Radio Electronics Kharkiv, Ukraine tsekhmistroroman@gmail.com

Serhii Shapovalov Department of MIRES Kharkiv National Universityof Radio Electronics Kharkiv, Ukraine serhii.shapovalov@nure.ua

3.0 at the chipset level, as well as very good indicators of power consumption, RF sensitivity and support for additional features such as DTMF detection / generation, audio file recording / playback, built-in POP3, SMTP protocols, MMS, FTP, HTTP, SSL, etc. Supported by GPRS multi-slot class 12 (\$\$5.6 Kbps).

The SIM800C module was created by SIMCom Wireless Solutions specifically taking into account the wishes of our customers and has dimensions of only 17.6 \* 15.7 mm and an LCC case with contacts along the perimeter, which implies the possibility of both manual and automated installation.

The Bluetooth transceiver in the module is implemented at the chipset level, so its presence does not affect the cost. Supports SPP, OPP, HFP profiles and work is underway to support additional profiles.

Figure 2 shows the module for determining the satellite coordinates of an object with a ceramic antenna, it has the parameters that are given below [3]:

Power Supply Range: 3 V to 5 V;

Model: GY-GPS6MV2;

Ceramic antenna;

EEPROM for saving the configuration data when powered off;

Backup battery;

LED signal indicator

Antenna Size: 25 x 25 mm.;

Module Size: 25 x 35 mm.;

Mounting Hole Diameter: 3 mm;

Default Baud Rate: 9600 bps.

Fig. 2. Module GPS-location Neo-8m ceramic antenna

NEO-6M GPS module with antenna and built-in EEPROM. This is compatible with various flight controller modules that provide GPS computer test software [3].

This board features the u-blox NEO-6M GPS module with antenna and built-in EEPROM. This is compatible with various flight controller boards designed to work with a GPS module.

### II. MAIN PARTS

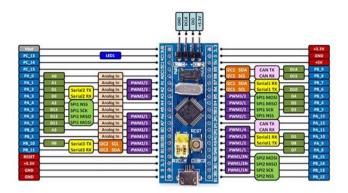

Let's consider further the option of using these modules to obtain a GPS location shown at Fig. 3.

Fig. 3. Application of a laboratory model for determining the geolocation of an object and transmitting their data via mobile communication based on arduino-uno

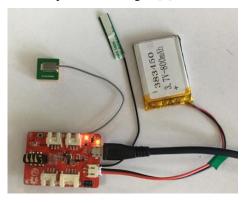

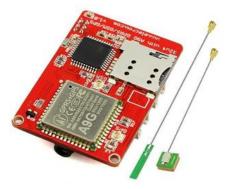

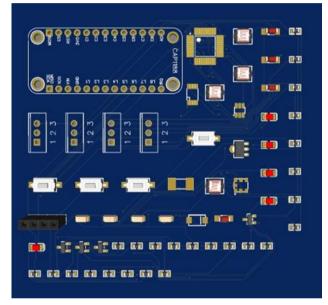

Overview module a9g-gsm/gprs/gps 32u4 (arduino leonardo). An alternative to the circuit shown in Fig. 3 is the industrial module presented in Fig. 4 [4].

Fig. 4. Module a9g-gsm/gprs/gps 32u4 view down

The 32U4 with A9g GPRS/GSM/GPS Board is based on Mega32U4 and A9 GPRS/GSM/GPS module.

Fig. 5. Module a9g-gsm/gprs/gps 32u4 view up

It can be used to make a call, send text messages and get GPS positioning. Also it has one analog interface, one IIC interface and two digital interface, which you can connect to other expansion modules. It is very easy for you to make a GPS Tracker by using this board. It is also very easy to use AT firmware and use several AT commands can be configured successfully. Two miniature coaxial RF connector is present on the back of the 32U4 with A9G GPRS/GSM/GPS Board to connect with a GSM antenna or a GPS antenna. The connector present on the 32U4 with A9G GPRS/GSM/GPS is called a U.FL connector [4]. The GSM Antenna supplied with the GPRS Shield has an SMA connector (and not an RP-SMA connector) on it. The connection topology is shown in the diagram below:

- ATMEGA32U4+A9G.

- Work voltage: 3.3V to 5V.

- Operating temperature:  $-30 \degree C$  to  $+80 \degree C$ .

- Three kinds of interfac.

- Equipped with 3.5mm headphone jack.

- 3.7V Battery power supply.

- Standby average current 3ma or less.

- Support the GSM / GPRS/ GPS Quad-band, including 850,900,1800,1900MHZ.

- Support China Mobile and China Unicom's 2G GSM network worldwide.

- GPRS Class 10.

- Sensitivity < -105.

- Support GPS Positioning.

- Support for voice calls.

- Support for SMS text messaging.

- Support GPRS data business, the maximum data rate: download 85.6Kbps, upload 42.8Kbps.

- Supports standard GSM07.07, 07.05 AT commands and Ai-Thinker extended commands.

- Supports two serial ports, a serial port to download an AT command port.

• Support for Global Positioning System.

Horizontal positioning accuracy of less than 2.5m.

- AT command supports the standard AT and TCP / IP command interface.

- Support digital audio and analog audio support for HR, FR, EFR, AMR speech coding.

The battery socket needs to be connected to 3.7V lithium battery, connected to GSM and GPS antenna, and the SIM card slot is inserted into the SIM card slot. Connect the computer to the circuit board via micro USB, as shown in the figure 4-5.

The following describes how to test the module.

Download the "a9\_serial\_test.ino" program file to the target board.

Open SSCOM32 serial debugging assistant, serial port baud rate :115200 bit/sec.

Test the GPS function. Remember to plug in the GPS antenna.

Send the following command:

- AT return OK;

- AT+GPS=1 return OK;

- -AT+GPSRD=1 return OK.

An example of testing the A9G module with the arduino platform is given below.

The test itself is implemented with a connected module via the computer's usb port. This test code complies with the Arduino development environment:

void setup()

{

Serial.begin(115200);

Serial1.begin(115200);

pinMode(4, OUTPUT);

pinMode(5, OUTPUT);

pinMode(8,OUTPUT);

digitalWrite(5, HIGH);

digitalWrite(4, LOW);

digitalWrite(8, HIGH);

delay(3000);

digitalWrite(8, LOW);

Serial.println("A9 Power ON!");

}

void loop()

}

}

```

{

```

char dat;

if(Serial1.available()){

dat = Serial1.read();

Serial.print(dat);

if(Serial.available()){

dat = Serial.read();

Serial1.print(dat);

}

### III. CONCLUSIONS

The overview of the characteristics of the specified microprocessor modules and ways of their use shows that their compatibility with ARDUINO platform and RASPBERRY PI also debugging kits - STM-32 kits. The example kit is STM-32-OPEN32L-D with STM-32 - Discovery. For example, STM-32 use in development of exclusive and pilot projects [5]. The modules under consideration have a wide range of use the A9G module combined with ARDUINO-LEONARDO platform despite the worst parameters of the antenna devises, has much smaller sizes than devises in figure 3. The size A9G module: 19.2\*18.8\*3 mm, size all module (fig.5) 45\*35 mm. The optimal way to use modules it is creation of tracking systems with GPS-tracks recording.

### REFERENCES

- M. Omarov, V. Kartashov and R. Tsekhmistro, "Features of the Use of Microprocessors in the Systems of Ovojectors in their Adaptation to the Conditions of the Former CIS", *I International Scientific and Practical Conference*, 2019. doi: 10.35598/mcfpga.2019.012.

- [2] Elecrow [Online]. Available: https://www.elecrow.com/wiki/index.php?title=GPRS/GSM\_Shield\_ v1.0http [Accessed: 1- Jun- 2021]

- [3] NEO-6\_DataSheet [Online]. Available: https://www.ublox.com/sites/default/files/products/documents/NEO-6\_DataSheet\_(GPS.G6-HW-09005).pdf [Accessed: 1- Jun- 2021]

- [4] Sensory [Online]. Available: https://www.sensory.com/wpcontent/uploads/80-0225-C.pdf [Accessed: 1- Jun- 2021]

- [5] Getting Started with A9G Low Power GSM/GPRS+GPS Module with Arduino [Online]. Available: https://how2electronics.com/a9ggsm-gprs-gps-module-with-arduino [Accessed: 1- Jun- 2021]

- [6] Waveshare. File:Open32L-D-Schematic. [Online]. Available: https:// www.waveshare.com/wiki/ Open32L-D [Accessed: 1- Jun- 2021]

# The Use of Intelligent Microprocessor Modules for Working with Sound Communication in the Development of Educational Equipment

Volodymyr Kartashov ORCID 0000-0001-8335-5373 Department of Natural Sciences Kharkiv National University of Radio Electronics Kharkiv, Ukraine volodymyr.kartashov@nure.ua

*Abstract*—This report is devoted to an overview of the technical characteristics and the specifics of the application of modern debugging microprocessor modules for recognizing audio and text signals.

Keywords—microcontroller system, RAM memory, EEPROM memory, RSC-4128 speech recognition processor

### I. INTRODUCTION

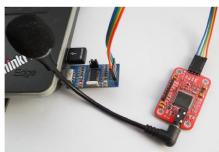

The success of modern technologies has made it possible to create intelligent microprocessor-based speech and sound recognition modules with built-in MEMS micro-phones and with traditional microphones that are connected. One of these modules is shown in Fig.1. It includes 4 microphones created using MEMS technology.

Fig. 1. Voice recognition module AC-108

Fig. 2 shows a plug-in microphone module. These appliances can be used in industrial devices. [1-2].

Fig. 2. Voice recognition module V3.1 Elechouse

Roman Tsekhmistro ORCID 0000-0003-3628-3658 Department of MIRES Kharkiv National University of Radio Electronics Kharkiv, Ukraine tsekhmistroroman@gmail.com

It has the following parameters: input memory can record 80 seconds sound voice of beep and put in EEPROM memory (storage without power supply). Before recognizing voice commands, they must be loaded from the storage memory (EEPROM) into the recognizer memory. RAM memory - the operative recognizer is designed for 7 voice commands, which means the module is able to simultaneously compare up to 7 voice commands with the incoming sound signal.

The module shown in Fig. 1 uses the RASPBERRY PI 40PIN interface, suitable for motherboards of the RASPBERRY PI series. There are 12 programmable full-color LEDs APA-102-2020 on the module board.

Raspberry Pi control interface: I2C, audio interface: I2S, Raspberry Pi drives the microphone array to capture voice via I2C interface, and then transmits the voice signal to the Raspberry Pi via I2S interface and finally 3.5mm headphones. basic / interface HDMI audio output.

The audio-wm8960 sound recognition module is shown in the Fig. 3.

Fig. 3. Voice recognition WM8960

1) Communication interface with minicomputer RASPBERRY Pi.

2) Levi and right MEMS microphone;

3) WM8960: low-power stereo codec;

4) Additional power. If the output is connected to a microphone, this micro USB provides sufficient current;

5) KF301-4P - left and right output channel of the speaker, pressure 2x1 W;

6) PH2.0-4 $\Pi$ : left and right output channel speaker, pressure 2x1 W;

7) Output to the headphones: pressure 40 MW (16 Ohm, 3.3V);

8) RGB LED: 3 APA102 color-coded LEDs, connected to SPI interface for Ruspberry Pi.

### II. MAIN PARTS

Consider further the ELECHOUSE V3 recognition module based on the RSC-4128 sound processor, since it has a removable microphone, which makes it possible to expand the practical aspects of its use [3-4]. In addition, there is information about the characteristics of this microphone:

- sensitivity: -38dB;

- load impedance: 2.2 kOhm;

- supply voltage: 3 V;

- frequency response: 100 Hz to 20 kHz.

The module is able to work without an external microcontroller, since the manufacturer has laid down functional independence, it is only necessary to record voice commands once and set the settings for independent operation using an external device (PC or MK).

To start working with the voice recognition module, we need to connect it either to a computer (we need a USB-UART connector Fig. 2), or to a microcontroller. If a microcontroller is used, it is necessary to develop a program code to control the module.

The principle of sound recording is associated with fast Fourier transform, creates an array of frequencies from time and then compares the input data with the available arrays. To train the module, the scheme shown in Fig. 2 is used. For the training process, a terminal program (Fig. 4) and instructions (commands) from the datasheet are used.

| Файл Редактор                                                                                               | Посмотреть | Монитор Ини     | струменты | Операции       | Справка  |       |                |     |

|-------------------------------------------------------------------------------------------------------------|------------|-----------------|-----------|----------------|----------|-------|----------------|-----|

| 60                                                                                                          | > 📃 🕇      | 60              |           |                |          |       |                |     |

| Terminal                                                                                                    | Monitor    |                 |           |                |          |       |                |     |

| Hex ab E                                                                                                    |            |                 |           |                |          |       |                |     |

| C<br>Speak now<br>Cl<br>Speak again<br>C<br>Success<br>Cl I .<br>C<br>ISpeak now<br>Cl<br>ISpeak again<br>C |            |                 |           |                |          |       |                |     |

| Success                                                                                                     |            |                 |           |                |          |       |                |     |

| el 11.                                                                                                      |            |                 |           |                |          |       |                |     |

| 1осл⇒ ⊛Нех                                                                                                  | O Cirele   | PlainText       | - 00      | Эттр. в реальн | -        |       |                | SI  |

| 00000000:AA 0                                                                                               | 5 30 01 02 | 83 A <u>C</u> I |           |                | ;01011   |       |                |     |

|                                                                                                             |            |                 |           |                |          |       |                |     |

| Comm Status                                                                                                 | CTS        | RING            | RLSD (CD) | CTS Hold       | DSR Hold | RLSD  | Hold XOF       | FHO |

| trenue                                                                                                      |            |                 |           |                | Tx 65 R  | 171 O | OM3(9600, N.8, | 1)0 |

Fig. 4. Application will write commands to module V3 c using the terminal program

Fig. 2 shows that 4 pins (IN0, IN1, IN2, GND) can be used to input the required groups of voice commands from storage into the voice command recognizer [3]. In order for the module to start recognizing voice commands after turning off and turning on the power, you need to specify which voice commands are required to be automatically loaded from the storage into the recognizer when power is applied. The OUT-0 ... .6 pins are designed to record the fact of recognition. It reacts to the recognition of the voice command in the 0-6 cell of the recognition device [3] RSC-4128 Overview presented Fig.5.

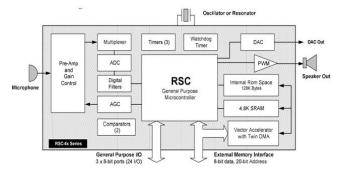

Fig. 5. Structura signal proseccor RSC-4128

The RSC-4128 operates in tandem with FluentChip firmware, an ultra compact suite of recognition and synthesis technologies [4]. The CPU core embedded in the RSC-4128 is an 8-bit, variable-length-instruction micro-controller. The instruction set is similar to 8051microcontroller, and has a variety of addressing mode, mov and 16 bit instructions.

The RSC-4128 has a high frequency (14,32 MHZ) clock as well as a low (32,768 Hz) clock. The RSC-4128 128 kbytes ROM, 16 bit ADC, 10bit DAC and micro-phone.

### **III.** CONCLUSIONS

A brief overview of the specifications of the specified microprocessor devices gives an opportunity for developers of experimental (exclusion) projects both scientific and industrial purpose to save time for development of the product.

Small overall dimensions and low energy consumption allows to actively use the designed module in projects type "Smart house" and others.

This fact is especially relevant because the modules are software and hardware compatible with the popular "Arduino" and "Rassberry" microcontrollers.

### REFERENCES

- M.A. Omarov, R.I. Tsekhmistro "Avtomatyzovana systema vidboru i teploviziyna diahnostika nezhyttyezdatnykh embrioniv v period inkubatsiyi yayets' sil'skohospodars'koyi ptytsi," Zbirnyk prats' II Mizhnarodnoyi konferentsiyi vyrobnytstvo y mekhatronni systemy..Kharkov, KHNURE, P. 35-38, 25-26 october, 2018.

- [2] Murad Omarov, Vladimir Kartashov, Roman Tsekhmistro. Features of the Use of Microprocessors in the Systems of Ovojectors in their Adaptation to the Conditions of the Former CIS. Theoretical and Applied Aspects of Device Development on Microcontrollers and FPGAs, MC&FPGA. – 2019. – P. 33-34. doi: 10.35598/mcfpga.2019.012.

- [3] Voice Recognition Module V3 [Online]. Available: http:// www elechouse.com /elechouse/images/product/VR3/ manual.pdf [Accessed: 1- Jun- 2021]

- [4] Speech recording [Online]. Available: https://www.sensory.com/wpcontent/uploads/80-0225-C.pdf [Accessed: 1- Jun- 2021]

MC&FPGA-2021

# Hardware of Monitoring the Identity of Operating Cycles of Diesel Generator

Oleksandr Yenikieiev ORCID 0000-0001-8633-3233 dept. Intelligent Decision Making Systems Donbass State Engineering Academy Kramatorsk, Ukraine yenikieiev@ukr.net

Dmitriy Zaharenkov ORCID 0000-0003-3951-022X dept. Intelligent Decision Making Systems Donbass State Engineering Academy Kramatorsk, Ukraine Dmit.zakharen@gmail.com

Abstract—It is offered to use a signal of fluctuations of speed of rotation of a cranked shaft at monitoring of identity of working cycles of the power unit. Hardware has been built and information technology for primary signal processing has been created. A deterministic mathematical model of a diesel circuit in the form of a mechanical system with four degrees of freedom under the condition of friction, Laplace transform, methods of similarity theory and signal graph theory, as well as the method of determinants is used in the development of algorithmic software. The monitoring procedure leads to the solution of a system of redefined algebraic equations with optimization of results based on the method of least squares.

### Keywords—fluctuation signal, information technology, algorithmic software, Laplace Transform

### I. INTRODUCTION

Technical and economic indicators of the diesel generator (DG) determine the setting of operating cycles [5], which depends on the uncertainty of setting the phases of gas distribution [6, 7]. The use of hardware for software setting of these phases allows to reduce the uncertainty of setting the identity of work cycles. Solving this problem will provide fuel savings of 5% [2] and reduce the likelihood of overloading individual cylinders. Therefore, the choice of the method of measuring the input information, construction of hardware and algorithmic monitoring of the identity of task.

### II. ANALYSIS OF LITERARY DATA

The authors propose the idea of monitoring the identity of the operating cycles of DG 3TD-1 based on the processing of data of indirect measurements. As a signal of measuring information, the authors chose fluctuations in the speed of rotation of the crankshaft. The results of studies of the signal of non-uniformity of rotation of the crankshaft DG 6NVD48UA are given in [4]. A measuring transducer and a method for calculating the average effective cylinder pressure, engine power, excess air ratio and exhaust gas temperature have been developed. In [3], a method was proposed to improve the control uncertainty of the fuel Liudmyla Nechvoloda ORCID 0000-0002-7584-6735 dept. Intelligent Decision Making Systems Donbass State Engineering Academy Kramatorsk, Ukraine lylyne4v@gmail.com

Katerina Krykunenko ORCID 0000-0003-1530-216X dept. Intelligent Decision Making Systems Donbass State Engineering Academy Kramatorsk, Ukraine ladybabenko87@ukr.net

supply process to the cylinders based on measurements of the amplitude of angular velocity oscillations and phase shifts of their extremes relative to the top dead center of the first cylinder. Reduces the effect of random interference on the information signal of the non-uniformity of the crankshaft rotation of the high-pass filter with a finite impulse response [1]. In this research the technique of processing of a signal of fluctuations with use of possibilities of the Matlab software environment is developed.

Known hardware and software tools for monitoring the identity of operating cycles have unsatisfactory metrological characteristics and low productivity of input information processing, as well as there is no algorithmic and applied software for processing indirect measurement data. The aim of research is to reduce the uncertainty of the hardware for measuring the signal of the crankshaft speed fluctuations and to improve the productivity of the process of estimating the identity of the working cycles of the DG.

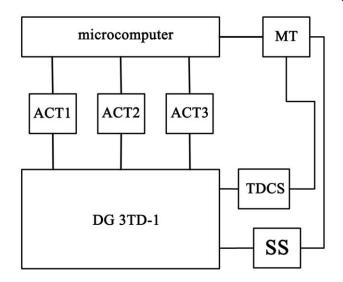

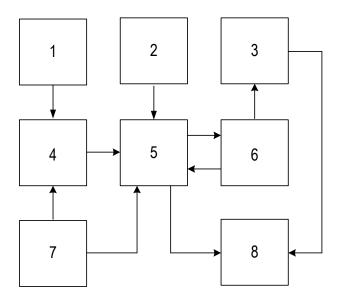

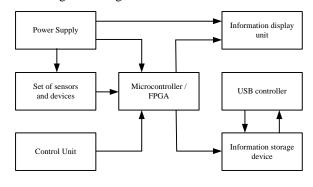

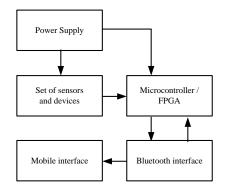

### III. CONSTRUCTION OF HARDWARE

The authors used electro-hydraulic injectors as actuators for adjusting the processes of fuel and air supply to the cylinders. Synchronization of the hardware with the phase of rotation of the crankshaft provides a signal of the top dead center of the first cylinder. The block diagram of the hardware for monitoring the identity of the operating cycles of the power unit based on the processing of data of indirect measurements is presented at Fig. 1. The architecture of the system consists of the following components: instantaneous crankshaft speed sensor (SS), top dead center sensor of the first cylinder (TDCS), measuring transducer (MT) of the fluctuation signal, microcomputer and three actuators (ACT1, ACT2 and ACT3).

Fig. 1. Hardware architecture

The procedure for monitoring the identity of the operating cycles of DG 3TD-1 involves the following actions:

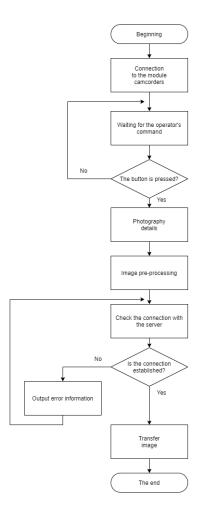

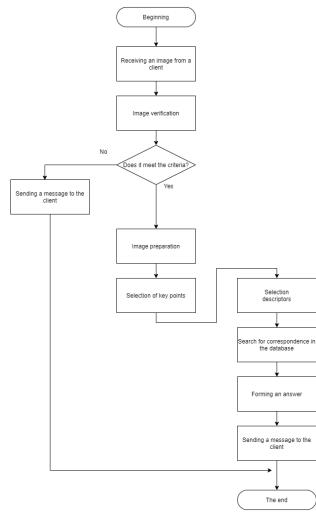

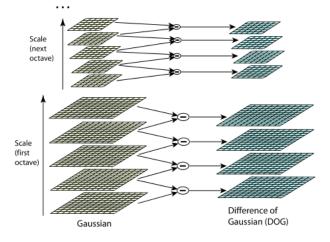

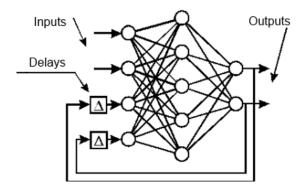

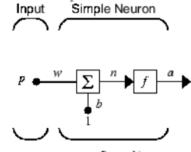

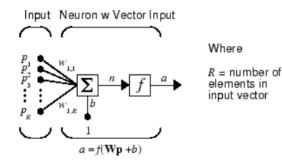

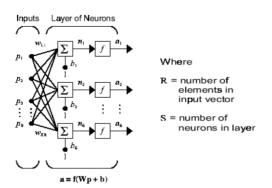

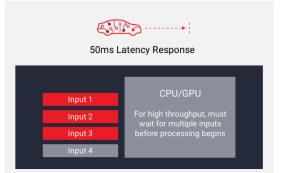

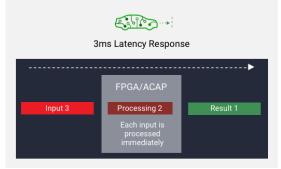

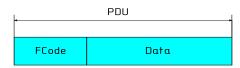

- measurement of the crankshaft speed signal;